Na continuação da construção do multiplicador 8×8, o objetivo desta etapa é construir em Verilog, um multiplicador de 4 bits utilizando o operador de multiplicação “*”, sintetizar e verificar sua operação.

O projeto resolvido desta etapa, pode ser baixado diretamente no github <clicando neste link aqui> e no diretório raiz IVER10_1 temos todos os arquivos e instruções dos exercícios.

Se você caiu de paraquedas por aqui e precisa saber como instalar o software Questa para trabalhar com Verilog, leia a série “Instalando Quartos com Questa”, <clicando neste link aqui>.

Continuando, passos A e B:

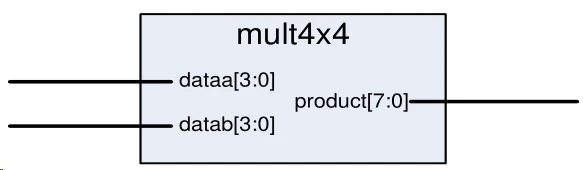

O exercício pede para baixar o diretório “lab 1b” e abrir o projeto no Quartus, que é o arquivo “mult4x4.qpf”, que em seguida pede para escrever o código de um multiplicador de 4 bits, conforme diagrama abaixo:

A descrição de hardware deste multiplicador é bastante simples, conforme indicado abaixo:

module mult4x4 (

input [3:0] dataa, datab,

output[7:0] product

);

assign product = dataa * datab;

endmodule

O nome do arquivo a ser salvo no diretório do projeto deve ser “mult4x4.v”. Caso estivéssemos programando, novamente seria comparável a um “hello world” ;-).

Caso minhas notas sejam de grande valia para ti, vou ficar muito agradecido se você clicar nos anúncios desta página e conferir o que meus patrocinadores tem para lhe oferecer.

Passo C:

O exercício pede para sintetizar o projeto clicando em “Start -> Start Analysis & Synthesis”. Erros de digitação devem ser entendidos e corrigidos até que o Quartus retorne a mensagem indicando que foi concluída com sucesso a análise e síntese do circuito. Não adianta prosseguir antes de concluir esta etapa.

Passo D:

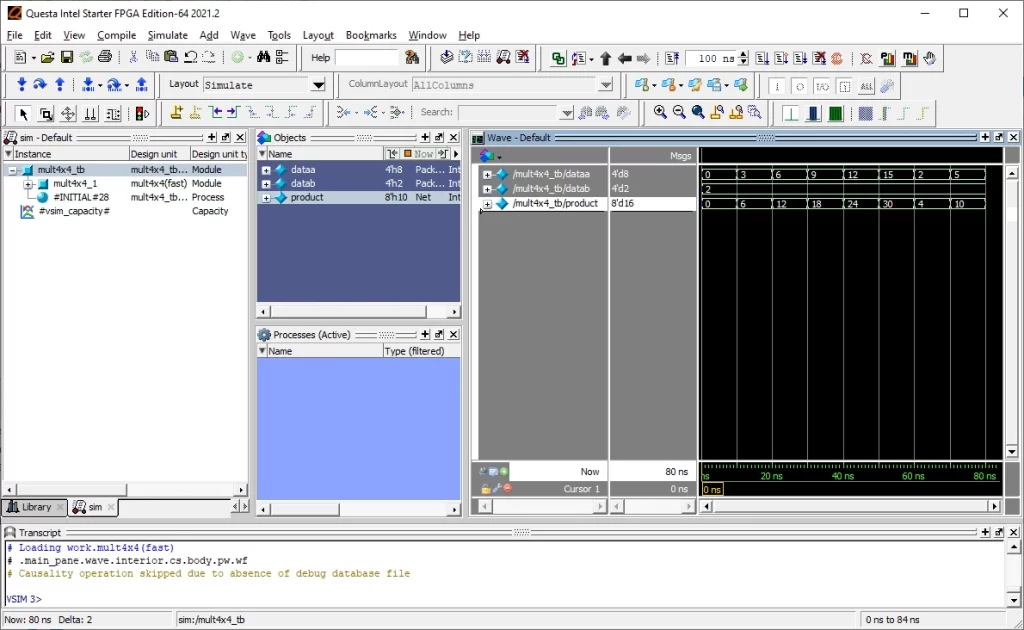

Nesta etapa o exercício pede para fazer uma simulação RTL usando o software ModelSim-Intel FPGA Edition. Nesta resolução vamos usar o Questa, que é a versão mais nova do ModelSim.

Da mesma forma que no exercício anterior, precisa iniciar o simulador Questa, clicando em “Iniciar” -> “Questa”, devendo aparecer a tela de abertura. Tem que fechar a tela “IMPORTANT Information” e clicar em “File” -> “Change Directory…” -> “navegar até a pasta do lab1b” -> clicar em no botão “Selecionar pasta”.

Este exercício lab1b, já vem com uma macro preparada na pasta lab1b, que é o arquivo mult4x4-tb.do.

Da mesma forma que no exercício anterior, precisa executar essa macro “mult4x4-tb.do” para executar a simulação. Isso deve ser feito no Questa, clicando no menu “Tools” -> “tcl” ->”Execute Macro” e em seguida selecionando o arquivo de macro “mult4x4-tb.do” e clicando no botão “Abrir”.

Aguarde a macro executar, leva cerca de 30 segundos. Uma vez executada a simulação definida pela macro, precisa clicar com o botão direito do mouse na tela preta “Wave – Default” e selecionar “Zoom Full”.

Após aplicar o zoom na tela Wave-Default, dá para notar que dataa vai variando, seu valor é multiplicado pelo valor 2 de “datab”, constante, e o resultado da multiplicação é apresentado em “product”, conforme indicado abaixo:

Implementando e testando na Mini-FPGA, o multiplicador 4×4

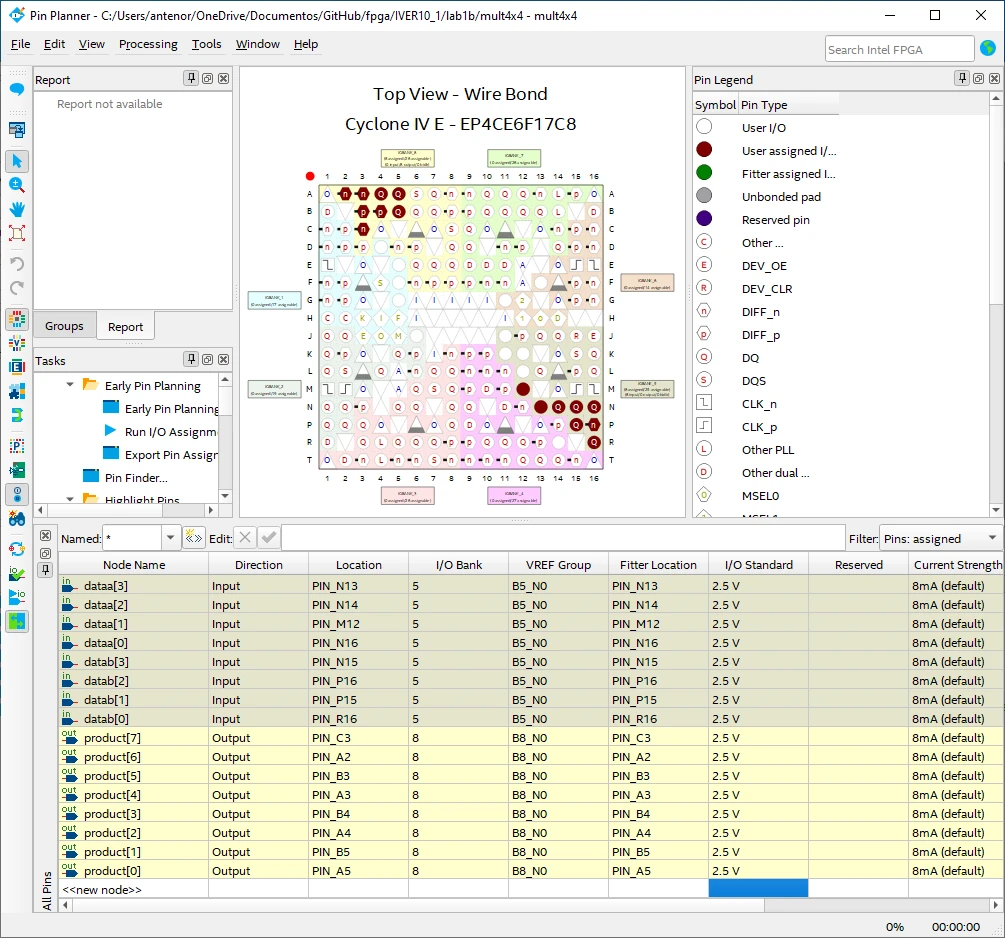

Os passos a seguir são específicos para a placa de desenvolvimento Mini-FPGA utilizando o Cyclone IV EP4CE6F17C8. Caso esteja utilizando outra placa de desenvolvimento, os devidos ajustes devem ser realizados.

- A placa de desenvolvimento precisaria de 4 chaves para receber a entrada de dataa e 4 chaves para datab.

- Também precisa de 8 leds para indicar o resultado da multiplicação.

- Os pinos de entrada e de saída devem ser indicados na etapa de pin assignment, de acordo com diagrama esquemático da placa Mini-FPGA.

- Leds 0 – 7 irão indicar o resultado da multiplicação e as 8 chaves irão suportar a entrada dos números a serem multiplicados.

Dito isso, basta abir a interface do Pin Planner do Questa, já configurada para o CycloneIV EP4CE6F17C8 e atribuir os pinos conforme a seguir:

| dataa[0] - PIN_N16 | dataa[1] - PIN_M12 | dataa[2] - PIN_N14 | dataa[3] - PIN_N13 | | datab[0] - PIN_R16 | datab[1] - PIN_P15 | datab[2] - PIN_P16 | datab[3] - PIN_N15 | | product[0] - PIN_A5 | product[1] - PIN_B5 | product[2] - PIN_A4 | product[3] - PIN_B4 | | product[4] - PIN_A3 | product[5] - PIN_B3 | product[6] - PIN_A2 | product[7] - PIN_C3 |

Figura abaixo mostra a interface do Pin Plannner e o mapeamento físico dos pinos:

Feita a atribuição dos pinos, basta compilar o projeto e gravar na Mini-FPGA <conforme abordado nesse link aqui>

- Multiplicador 8×8: Exercício lab1a somador 16bits

- Multiplicador 8×8: Exercício lab1b multiplicador 4 bits <-

- Multiplicador 8×8: Exercício lab2a 4-bits 2:1 Mux

- Multiplicador 8×8 Exercício lab2b 8-16bit left regb

- Multiplicador 8×8 Exercício lab3 Display 7 segmentos

- Multiplicador 8×8 Exercício lab4a Registrador 16bits

- Multiplicador 8×8 Exercício lab4b Contador 2bits assíncrono

- Multiplicador 8×8 Exercício lab5a State Machine

- Multiplicador 8×8 Exercício lab5b Montagem final

Realizado por Renato de Pierri em 26/11/2023

Fonte: Manual de exercícios de Introdução ao Verilog, da Intel.