Na continuação da construção do multiplicador 8×8, o objetivo desta etapa é construir em Verilog, um “8 bits to 16 bits left shift register” (registrador de deslocamento à esquerda de 8 para 16 bits), utilizando a cláusula de controle “if-else”, sintetizar e verificar sua operação.

O projeto resolvido desta etapa, pode ser baixado diretamente no github <clicando neste link aqui> e no diretório raiz IVER10_1 temos todos os arquivos e instruções dos exercícios.

Se você caiu de paraquedas por aqui e precisa saber como instalar o software Questa para trabalhar com Verilog, leia a série “Instalando Quartus com Questa”, <clicando neste link aqui>.

Continuando, passos A e B:

A instrução pede para abrir o Quartus, navegar até a pasta lab2b, selecionar e abrir o arquivo “shifter.qpf”.

Caso o projeto indique alguma incompatibilidade de versão e ou chip, faça as devidas correções no caminho de configuração “Assignments” ->”Device” e “Assignments” ->”Device” -> “Device and Pin Options” de acordo com sua placa de desenvolvimento, conforme explicado no primeiro exercício desta sequência, <mais detalhes, clicando aqui>.

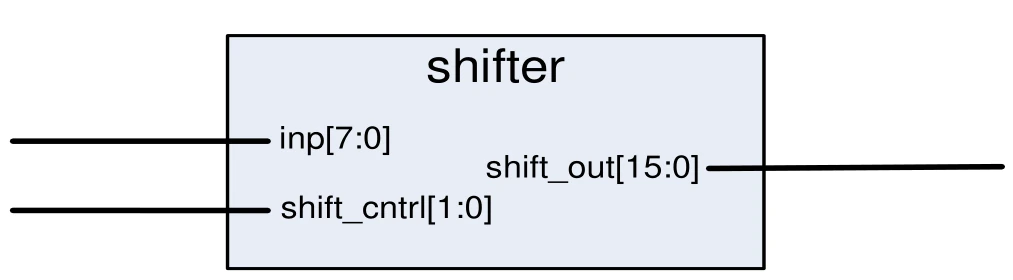

Em seguida o exercício pede para escrever a descrição de hardware do bloco “8 bits to 16 bits left shift register”, conforme está indicado na figura abaixo e especificado a seguir:

- Crie no projeto um novo arquivo Verilog, clicando em “File” -> “New” -> “Verilog HDL File”.

- Escreva o código do “8 bits to 16 bits left shift register”, usando a declaração behavioral statement (declaração comportamental) do tipo “if-else”, com as seguintes características:

- Quando “shift_ctrl” é “0” ou “3”, não há deslocamento. O “shift_out[7:0]” é igual a “input[7:0]” e todos os outros bits ficam com o valor zero.

- Quando “shift_ctrl” é 1, então a entrada é deslocada para esquerda em 4 bits dentro do “shift_out”. O “shift_out[11:4]” recebe o valor de “input[7:0]” enquanto todos os outros bits são “0”.

- Quando “shift_ctrl” é 2, então a entrada é deslocada para esquerda em 8 bits no “shift_out”. “shift_out[15:8]” recebe o valor de “input[7:0]” enquanto todos os outros bits são “0”.

- Quando “shift_ctrl” é 2, então a entrada vai deslocar para a esquerda em 8 bits no “shift_out”. O “shift_out[15:8]” recebe o valor de “input[7:0]” enquanto todos os outros bits ficam com o valor zero. Utilize nomes no diagrama acima para nomear seu bloco e suas portas, todos em caixa baixa.

- Note que codificar com behavioral statements (declarações comportamentais) sempre requer o uso do bloco procedural.

- Todas entradas do bloco procedural devem declaradas na lista de eventos do bloco.

- Tente simplificar suas escolhas quando possível, reconhecendo similaridades entre as escolhas.

Caso minhas notas sejam de grande valia para ti, vou ficar muito agradecido se você clicar nos anúncios desta página e conferir o que meus patrocinadores tem para lhe oferecer.

Um exemplo de código resolvido segue abaixo:

module shifter( input [7:0] inp, input [1:0] shift_cntrl, output reg [15:0] shift_out ); // Tornando todas entradas sensíveis ao evento: always@(inp, shift_cntrl) begin if (shift_cntrl == 2'b01) shift_out = (inp << 4); else if (shift_cntrl == 2'b10) shift_out = (inp << 8); else shift_out = inp; end endmodule

Salve o arquivo como “shifter.v”, dentro da pasta “lab2b” do diretório do projeto.

Passo C, Sintetizando e corrigindo o código:

O exercício pede para sintetizar o projeto clicando em “Start -> Start Analysis & Synthesis”. Erros de digitação devem ser entendidos e corrigidos até que o Quartus retorne a mensagem indicando que foi concluída com sucesso a análise e síntese do circuito. Não adianta prosseguir antes de concluir esta etapa.

Passo D, Proceda com a simulação RTL:

Nesta etapa o exercício pede para fazer uma simulação RTL usando o software ModelSim-Intel FPGA Edition.

Nesta resolução vamos usar o Questa, que é a versão mais nova do ModelSim. Precisa iniciar o simulador Questa, clicando em “Iniciar” -> “Questa”.

Na tela do Questa: “File” -> “Change Directory…” -> “navegar até a pasta do lab2b” -> clicar em no botão “Selecionar pasta”.

Este exercício lab2b, já vem com uma macro preparada na pasta lab2b, que é o arquivo shifter_tb.do.

Para fazer a simulação, precisa executar a macro “shifter_tb.do”. Isso deve ser feito, clicando no menu “Tools” -> “tcl” -> ”Execute Macro” e em seguida selecionando o arquivo de macro “shifter_tb.do”, e clicando no botão “Abrir”.

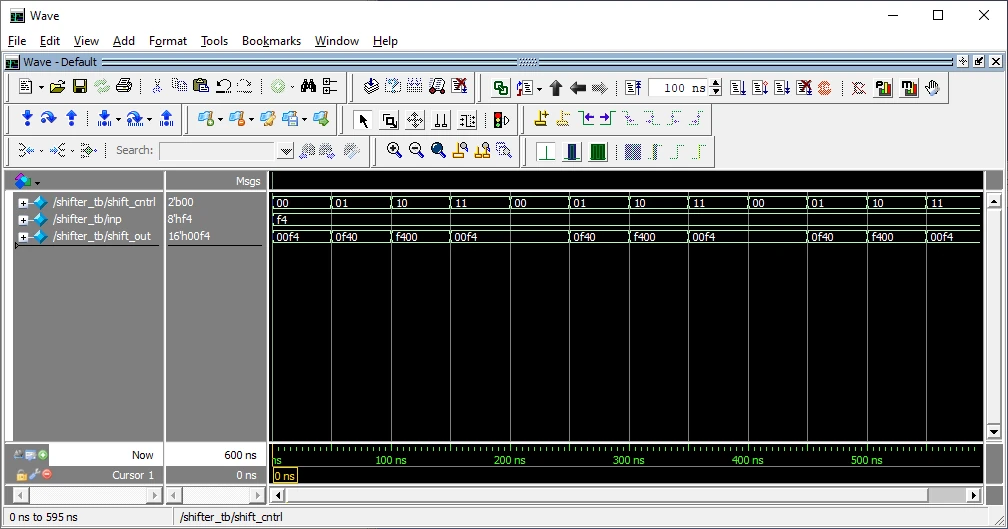

A macro “shifter_tb.do” será executada, abrindo a tela com o resultado da simulação.

Na tela do resultado da simulação, precisa com o botão direito do mouse na tela preta “Wave – Default” e selecionar “Zoom Full” de modo a expandir o resultado da simulação na tela “Wave-Default”, conforme indicado na imagem e na tabela abaixo:

| shift_ctrl | input | shift_out |

|---|---|---|

| 00 | 0xf4 | 0x00f4 |

| 01 | 0xf4 | 0x0f40 |

| 10 | 0xf4 | 0xf400 |

| 11 | 0xf4 | 0x00f4 |

Caso a simulação não fique conforme apresentado acima, precisa proceder com a revisão do exercício.

Implementando e testando na Mini-FPGA, o registrador de deslocamento à esquerda de 8 para 16 bits.

Os passos a seguir são específicos para a placa de desenvolvimento Mini-FPGA utilizando o Cyclone IV EP4CE6F17C8.

Caso esteja utilizando outra placa de desenvolvimento, os devidos ajustes devem ser realizados.

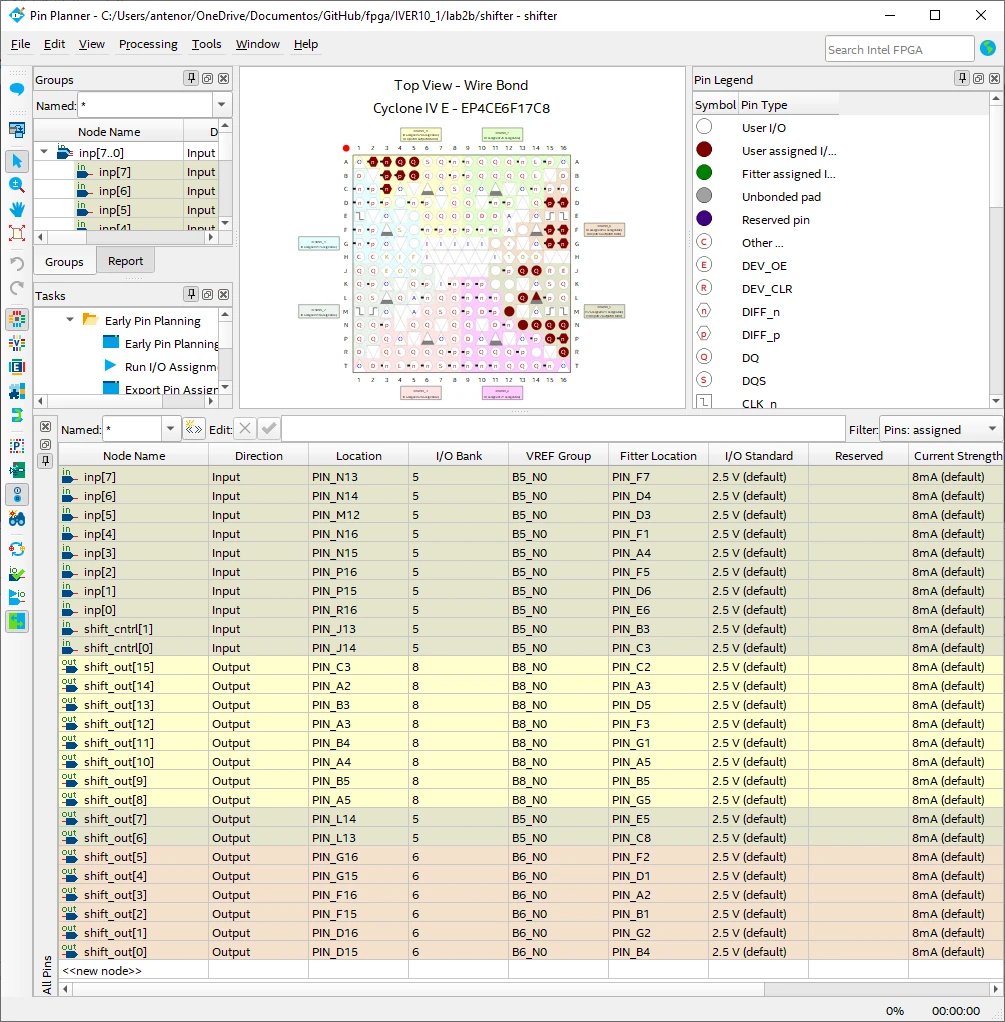

Para testar o registrador de deslocamento à esquerda de 8 para 16 bits (8x16bits left shift register), é necessário mapear no pin-planner, de acordo com o hardware da placa Mini-FPGA:

- 8 chaves para o sinal de entrada “inp[7:0]”

- 16 leds para a saída “shift_out[15:0]”

- 2 chaves para o sinal “shift_cntrl[1:0]”

Que deve ficar configurado conforme abaixo e print de tela do pin-planner:

| inp[0] - PIN_R16 | inp[1] - PIN_P15 | inp[2] - PIN_P16 | inp[3] - PIN_N15 | | inp[4] - PIN_N16 | inp[5] - PIN_M12 | inp[6] - PIN_N14 | inp[7] - PIN_N13 | | shift_out[ 0] - PIN_D15 | shift_out[ 1] - PIN_D16 | shift_out[ 2] - PIN_F15 | shift_out[ 3] - PIN_F16 | | shift_out[ 4] - PIN_G15 | shift_out[ 5] - PIN_G16 | shift_out[ 6] - PIN_L13 | shift_out[ 7] - PIN_L14 | | shift_out[ 8] - PIN_A5 | shift_out[ 9] - PIN_B5 | shift_out[10] - PIN_A4 | shift_out[11] - PIN_B4 | | shift_out[12] - PIN_A3 | shift_out[13] - PIN_B3 | shift_out[14] - PIN_A2 | shift_out[15] - PIN_C3 | | shift_cntrl[1] - PIN J13 | shift_cntrl[0] - PIN J14 |

Tela do pin planner:

Terminada a etapa acima, fechar a janela do pin planner, compilar o projeto, fazer o upload do código no FPGA e testar o funcionamento do shift register que deve se comportar de acordo com a tabela binária abaixo:

| shift_ctrl | input | shift_out |

|---|---|---|

| 00 | <valor de inp [0:7]> | 00000000<valor de inp [0:7]> |

| 01 | <valor de inp [0:7]> | 0000<valor de inp [0:7]>0000 |

| 10 | <valor de inp [0:7]> | <valor de inp [0:7]>00000000 |

| 11 | <valor de inp [0:7]> | 00000000<valor de inp [0:7]> |

Resumo deste exercício:

Foi descrito e simulado um bloco de shift register de 8 para 16 bits de deslocamento à esquerda utilizando o “statement behavioral”.

- Multiplicador 8×8: Exercício lab1a somador 16bits

- Multiplicador 8×8: Exercício lab1b multiplicador 4 bits

- Multiplicador 8×8: Exercício lab2a 4-bits 2:1 Mux

- Multiplicador 8×8 Exercício lab2b 8-16bit left regb <-

- Multiplicador 8×8 Exercício lab3 Display 7 segmentos

- Multiplicador 8×8 Exercício lab4a Registrador 16bits

- Multiplicador 8×8 Exercício lab4b Contador 2bits assíncrono

- Multiplicador 8×8 Exercício lab5a State Machine

- Multiplicador 8×8 Exercício lab5b Montagem final

Publicado por Renato de Pierri em 30/11/2023.

Fonte: Manual de exercícios de Introdução ao Verilog, da Intel.