Na continuação da construção do multiplicador 8×8, o objetivo desta etapa é construir em Verilog, um multiplexador de 4 bits 2:1, utilizando a cláusula de controle “if-else”, sintetizar e verificar sua operação. O projeto resolvido desta etapa, pode ser baixado diretamente no github <clicando neste link aqui> e no diretório raiz IVER10_1 temos todos os arquivos e instruções dos exercícios.

Se você caiu de paraquedas por aqui e precisa saber como instalar o software Questa para trabalhar com Verilog, leia a série “Instalando Quartus com Questa”, <clicando neste link aqui>.

Continuando, passos A e B:

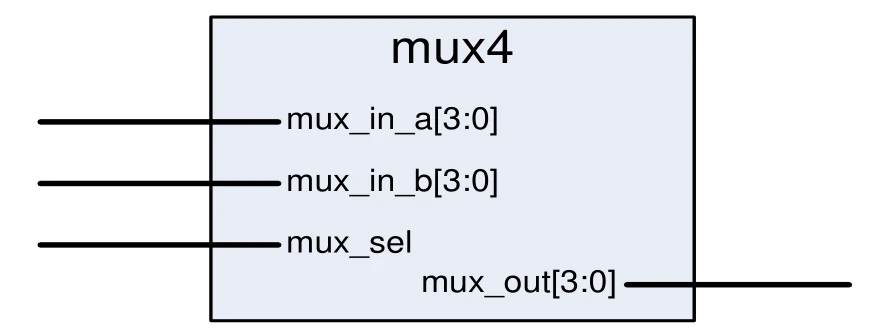

A instrução pede para abrir o Quartus, navegar até a pasta lab2a, selecionar e abrir o arquivo mux4.qpf e em seguida pede para escrever a descrição de hardware do bloco multiplexador 2:1, conforme indicado na figura abaixo:

O multiplexador deve ter:

- 2 entradas de 4 bits: “mux_in_a[3:0]”, “mux_in_b[3:0].

- Uma linha de seleção “mux_sel”.

- Uma linha de saída com 4 bits “mux_out[3:0]”.

- Quando “mux_sel” tiver valor lógico zero, ele deve apresentar a entrada “mux_in_a[3:0]” em “mux_out[3:0]”.

- Quando “mux_sel” tiver valor lógico um, ele deve apresentar a entrada “mux_in_b[3:0]” em “mux_out[3:0]”.

- A codificação com declarações de comportamento “behavioral”, sempre requer o uso de blocos “block”.

- Todas entradas do bloco procedural, devem ser listadas na lista de monitoramento de eventos do bloco.

Código criado para o multiplexador:

module mux4( input [3:0] mux_in_a, mux_in_b, input mux_sel, output reg[3:0] mux_out ); //Criando processo sensivel a todas entradas always@(mux_in_a, mux_in_b, mux_sel) begin if (mux_sel == 1'b0) mux_out = mux_in_a; else mux_out = mux_in_b; end endmodule

Passo C: Sintetizando o projeto e corrigindo erros.

Uma vez criado o bloco, salve como mux4.v, no diretório do exercício lab2a, mande sintetizar e vá corrigindo os erros até que retorne a mensagem “Quartus Prime Analysis & Synthesis was successful”.

Passo D: Executando a simulação RTL:

Como nos exercícios anteriores, é para abrir o Questa e mudar para o diretório do exercício, que no caso é o lab2a.

Clique em “Tools” -> “Tcl” -> “Execute macro”, selecione o arquivo “mux4_tb.do” e clique em “Abrir”.

Neste momento o diretório work será adicionado à lista de arquivos e em seguida será aberta a janela do “Quarter Intel Starter FPGA Edition”.

Na área da janela “Wave – Default”, clique com o botão direito do mouse sobre a área das formas de onda e selecione a opção “Zoom Full”.

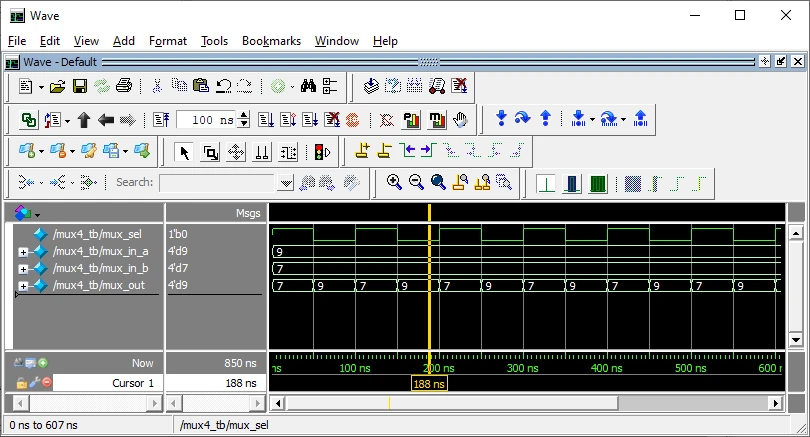

Observe na tela “Wave – Default”, que “mux_out” irá apresentar o valor, de acordo com a seleção de “mux_sel”, conforme indicado na tabela abaixo:

| mux_sel | mux_in_a | mux_in_b | mux_out |

|---|---|---|---|

| 0 | 9 | 7 | 9 |

| 1 | 9 | 7 | 7 |

Caso a simulação não fique conforme apresentado na figura acima, precisa proceder com a revisão do exercício.

Implementando e testando na Mini-FPGA, o multiplexador de 4 bits 2:1

Os passos a seguir são específicos para a placa de desenvolvimento Mini-FPGA utilizando o Cyclone IV EP4CE6F17C8.

Caso esteja utilizando outra placa de desenvolvimento, os devidos ajustes devem ser realizados.

Para testar o módulo do multiplexador de 4 bits 2:1, são necessários:

- 4 chaves para o sinal “mux_in_a[3:0]”

- 4 chaves para o sinal “mux_in_b[3:0]”

- 1 botão binário “mux_sel” para selecionar qual entrada irá aparecer na saída.

- 4 saídas led para o sinal “mux_out[3:0]”

Quando o botão “mux_sel” estiver em zero, “mux_out[3:0]” irá apresentar o sinal “mux_in_a[3:0]”.

Quando o botão “mux_sel” estiver em um, “mux_out[3:0]” irá apresentar o sinal “mux_in_b[3:0]”.

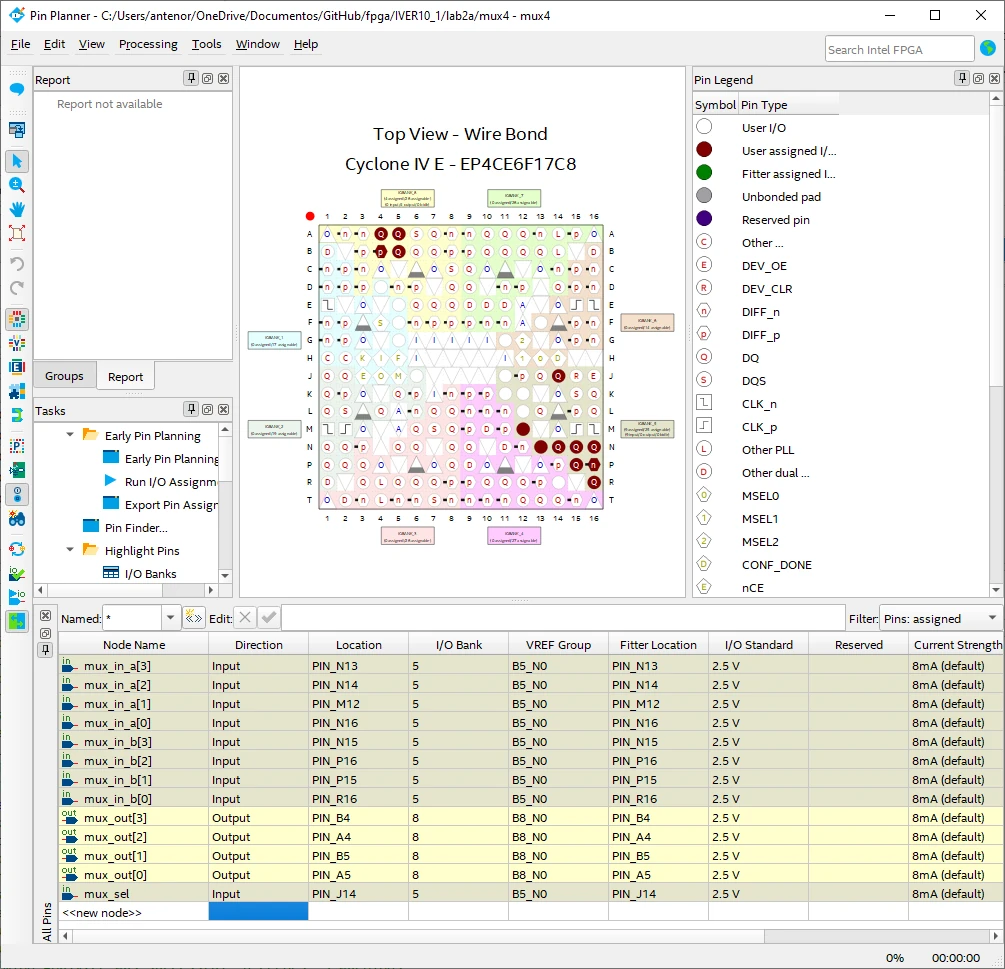

Dito isso, é hora de abir a interface do Pin Planner do Questa, já configurada para CycloneIV EP4CE6F17C8 e atribuir os pinos de acordo com o layout de hardware da placa Mini-FPGA, conforme lista a seguir:

| mux_in_a[0] - PIN_N16 | mux_in_a[1] - PIN_M12 | mux_in_a[2] - PIN_N14 | mux_in_a[3] - PIN_N13 | | mux_in_b[0] - PIN_R16 | mux_in_b[1] - PIN_P15 | mux_in_b[2] - PIN_P16 | mux_in_b[3] - PIN_N15 | | mux_out[0] - PIN_A5 | mux_out[1] - PIN_B5 | mux_out[2] - PIN_A4 | mux_out[3] - PIN_B4 | | mux_sel - PIN J14 |

O pin planner deve ficar conforme figura abaixo:

Fechar a janela do pin-planner, compilar o projeto, fazer o upload do código no chip e testar o funcionamento do mux.

- Quando “Key 0″ estiver em nível lógico 1 (solta), mux_out[3:0]” irá apresentar o valor das chaves de “mux_in_b[3:0]”

- Quando “Key 0″ estiver em nível lógico 0 (acionada), mux_out[3:0]” irá apresentar o valor das chaves de “mux_in_a[3:0]”

- Multiplicador 8×8: Exercício lab1a somador 16bits

- Multiplicador 8×8: Exercício lab1b multiplicador 4 bits

- Multiplicador 8×8: Exercício lab2a 4-bits 2:1 Mux <-

- Multiplicador 8×8 Exercício lab2b 8-16bit left regb

- Multiplicador 8×8 Exercício lab3 Display 7 segmentos

- Multiplicador 8×8 Exercício lab4a Registrador 16bits

- Multiplicador 8×8 Exercício lab4b Contador 2bits assíncrono

- Multiplicador 8×8 Exercício lab5a State Machine

- Multiplicador 8×8 Exercício lab5b Montagem final

Publicado por Renato de Pierri em 28/11/2023.

Fonte: Manual de exercícios de Introdução ao Verilog, da Intel.