Na continuação da construção do multiplicador 8×8, agora que temos todos os blocos necessários para completar o multiplicador, o objetivo desta etapa é é fazer a montagem final do mesmo, integrando todos os módulos desenvolvidos nos passos anteriores, utilizando o instanciamento e modelagem estrutural do Verilog. Também iremos sintetizar e verificar a sua operação.

O projeto resolvido desta etapa, pode ser baixado diretamente no github <clicando neste link aqui> e no diretório raiz IVER10_1 temos todos os arquivos e instruções dos exercícios.

Se você caiu de paraquedas por aqui e precisa saber como instalar o software Questa para trabalhar com Verilog, leia a série “Instalando Quartus com Questa”, <clicando neste link aqui>.

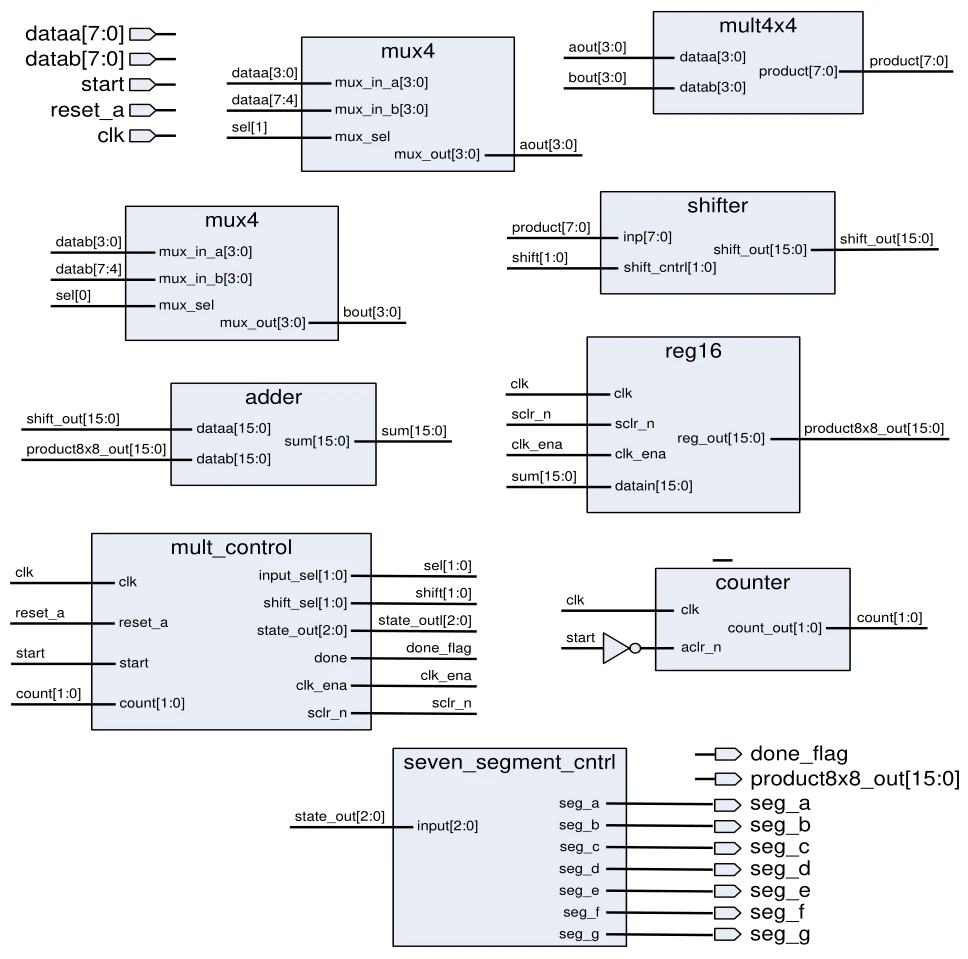

Partindo dos blocos que foram montados nos passos anteriores, é hora de instanciar cada um dos componentes em um design (projeto) alto nível e fazer a conexão de todos os sinais conforme diagrama abaixo:

Passos A e B:

Abra o projeto multiplicador 8×8. No software Intel Quartus Prime, vá para o menu “File” e escolha Abrir projeto que é o arquivo “mult8x8.qpf” e ele fica na pasta “lab5b”.

Crie um arquivo para Verilog para instanciar os componentes do multiplicador. Com o Quartus aberto, clique em “File” -> “New” -> “Verilog HDL File” -> “Ok”. O editor de texto do Quartus irá abrir.

Escreva o código-fonte para conectar o multiplicador 8×8 usando instanciações estruturais do Verilog, tendo como guia as seguintes informações:

- Declare um módulo de nível superior denominado mult8x8 com as portas de nível superior conforme exibido na figura acima.

- Crie duas instâncias do “mux4” (2 cópias), “mult4x4”, “shifter”, “contador”, “mult_control”, “reg16”, e de “somador e seven_segment_cntrl”, com base nas conexões mostradas na figura acima.

- Utilize “u6” como o nome da instância de “multi_control”. Para os outros módulos, use qualquer nome de instância que desejar.

- Para executar os passos acima, seré necessário declarar novos fios internos para as conexões entre os blocos. Utilizar a mesma nomenclatura da figura acima.

- Salve o arquivo criado com o nome mult8x8.v, no diretório lab5b do projeto.

Caso minhas notas sejam de grande valia para ti, vou ficar muito agradecido se você clicar nos anúncios desta página e conferir o que meus patrocinadores tem para lhe oferecer.

Passo C, Sintetizando:

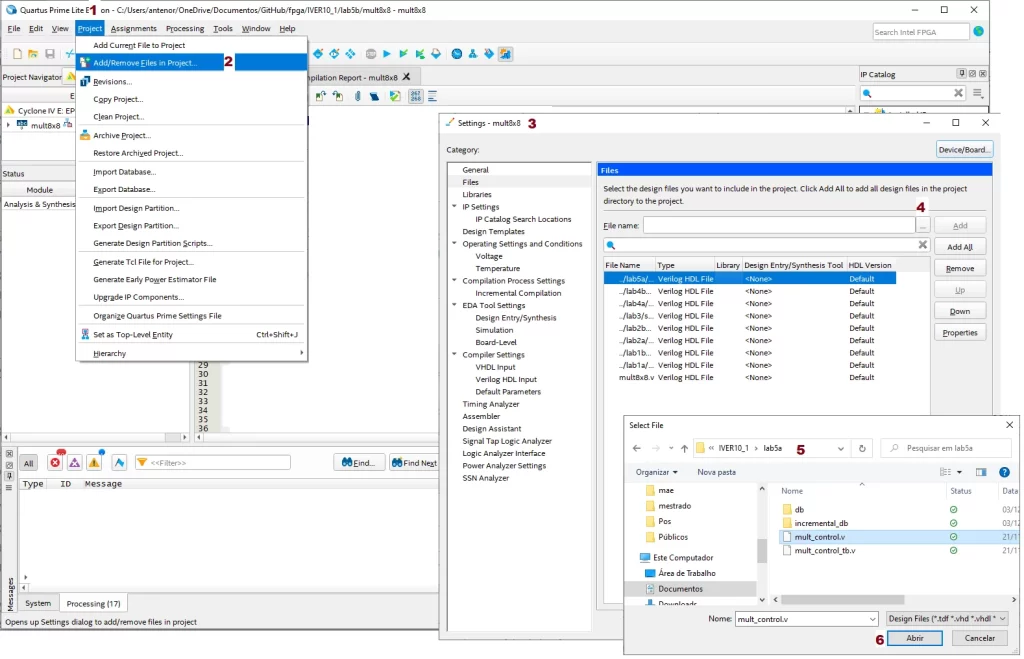

Como os arquivos fonte dos módulos que este projeto irá utilizar foram desenvolvidos em diretórios diferentes, antes de sintetizar o projeto é necessário adicionar esses arquivos diretamente ao projeto.

Conforme indicado na figura abaixo, para adicionar os arquivos que faltam, vá no menu “Project” (1), selecione “Add/Remove files” (2) para abrir a tela “Settings” (3). Clique no “…” (4) e navegue até cada um dos subdiretórios utilizados nos exercícios 1 até o 5a (5), e vá adicionando cada um dos arquivos necessários a este projeto (6) e clique em “Apply” -> “Ok” para fechar a tela “Settings”.

A tabela abaixo contém a lista dos arquivos que devem ser adicionados:

| Adicionar no projeto, os seguintes arquivos: | |

|---|---|

| Arquivo | Laboratório |

| adder.v | lab1a |

| mult4x4.v | lab1b |

| mux4.v | lab2a |

| shifter.v | lab2b |

| seven_segment_cntrl.v | lab3 |

| reg16.v | lab4a |

| counter.v | lab4b |

| mult_control.v | lab5a |

Segue um exemplo da construção do código.

// Inicio da declaracao dos modulos top-level "mult8x8" module mult8x8 ( input start, reset_a, clk, input [7:0] dataa, datab, output seg_a, seg_b, seg_c, seg_d, output seg_e, seg_f, seg_g, done_flag, output [15:0] product8x8_out ); // Declarando fios de conexão entre os blocos wire [3:0] aout, bout; wire [7:0] product; wire [15:0] shift_out, sum; wire [1:0] count, shift; wire [2:0] state_out; wire clk_ena, sclr_n; wire [1:0] sel; //Interligando os blocos do esquematico mux4 u1 (.mux_in_a(dataa[3:0]), .mux_in_b(dataa[7:4]), .mux_sel(sel[1]), .mux_out(aout)); mux4 u2 (.mux_in_a(datab[3:0]), .mux_in_b(datab[7:4]), .mux_sel(sel[0]), .mux_out(bout)); mult4x4 u3 (.dataa(aout), .datab(bout), .product(product)); shifter u4 (.inp(product), .shift_cntrl(shift), .shift_out(shift_out)); counter u5 (.clk(clk), .aclr_n(!start), .count_out(count)); mult_control u6 (.clk(clk), .reset_a(reset_a), .start(start), .count(count), .input_sel(sel), .shift_sel(shift), .state_out(state_out), .done(done_flag), .clk_ena(clk_ena), .sclr_n(sclr_n)); reg16 u7 (.clk(clk), .sclr_n(sclr_n), .clk_ena(clk_ena), .datain(sum), .reg_out(product8x8_out)); adder u8 (.dataa(shift_out), .datab(product8x8_out), .sum(sum)); seven_segment_cntrl u9 (.inp(state_out), .seg_a(seg_a), .seg_b(seg_b), .seg_c(seg_c), . seg_d(seg_d), .seg_e(seg_e), .seg_f(seg_f), .seg_g(seg_g)); endmodule

Execute o comando para sintetizar o projeto. Vá corrigindo quaisquer erros e avisos até que o sistema retorne a mensagem “Analysis & Sunthesis was Successfull.”.

Passo D: Realizando a simulação RTL:

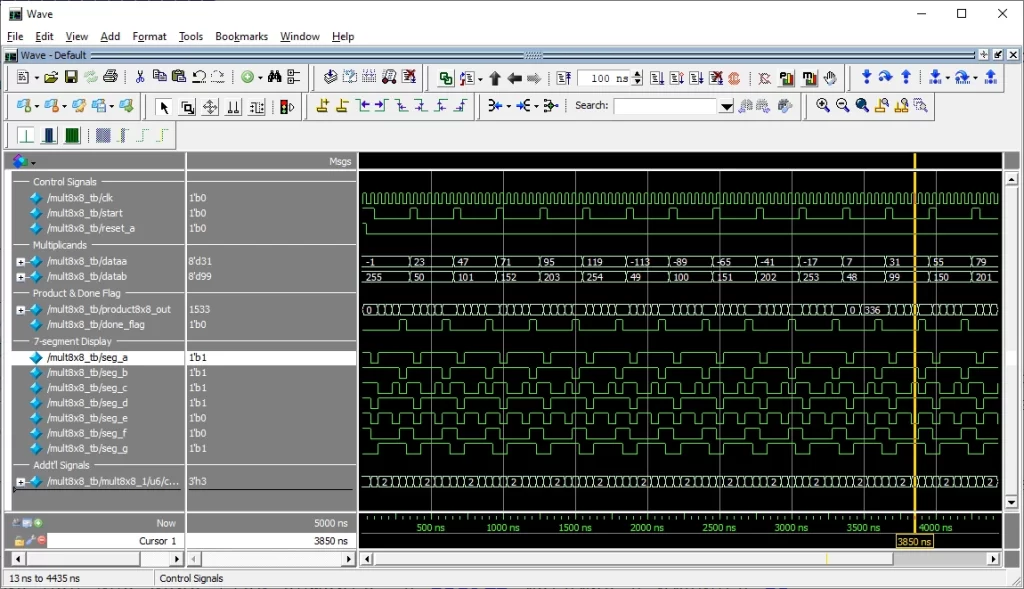

Nesta etapa vamos simular a funcionalidade do projeto do multiplicador que foi desenvolvido utilizando o software Questa, na seguinte sequência:

- Iniciar o Questa

- Mudar para o diretório do projeto, que no caso é o diretório “lab5b”: “File” -> “Change Directory” -> navegar até a pasta “lab5b” e clicar em “Selecionar a pasta”.

- Clicar em “Tools” -> “Tcl” -> “Execute Macro” -> selecionar o arquivo de macro “mult8x8_tb.do” e clicar em “Abrir”.

Ao clicar em abrir, esse arquivo de macro irá chamar o arquivo de testbench “mult8x8_tb.v” que tem os parâmetros de testes do multiplicador e deve apresentar a tela de simulação abaixo:

Use a ferramenta Zoom In para ampliar até poder ver a saída “product8x8_out” mostrando o cálculo da multiplicação dos valores “dataa” e “datab”, na subida da flag “done_flag”, conforme indicado acima (cada vez que “done_flag” é alto, o resultado é apresentado na saída “product8x8_out”).

Caso a saída não se comporte conforme acima, revise as etapas anteriores e assegure que estão funcionando ok, inclusive os outros exercícios desta série.

Sumário desta etapa:

Elaborada a codificação em alto nível do multiplicador 8×8 utilizando modelagem estrutural e instanciamento de componentes e por fim, foi realizada a simulação do código Verilog, empregando a ferramenta Questa.

- Multiplicador 8×8: Exercício lab1a somador 16bits <-

- Multiplicador 8×8: Exercício lab1b multiplicador 4 bits

- Multiplicador 8×8: Exercício lab2a 4-bits 2:1 Mux

- Multiplicador 8×8 Exercício lab2b 8-16bit left regb

- Multiplicador 8×8 Exercício lab3 Display 7 segmentos

- Multiplicador 8×8 Exercício lab4a Registrador 16bits

- Multiplicador 8×8 Exercício lab4b Contador 2bits assíncrono

- Multiplicador 8×8 Exercício lab5a State Machine

- Multiplicador 8×8 Exercício lab5b Montagem final <-

Publicado por Renato de Pierri em 03/12/2023

Fonte: Manual de exercícios de Introdução ao Verilog, da Intel.