Esta resolução é baseada no curso Introdução ao Verilog que fiz pela Intel e tem por objetivos: Não me deixar esquecer o que aprendi e construir um multiplicador 8×8 sequencial, conforme descrito a seguir:

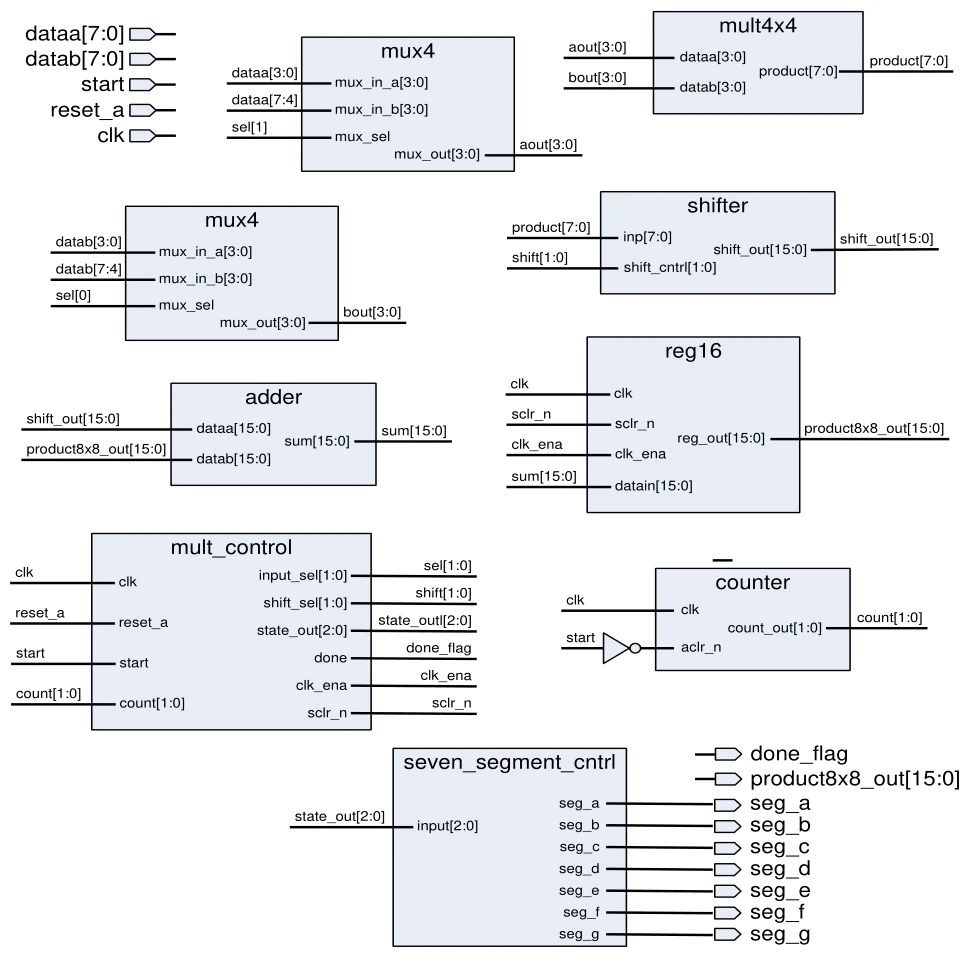

- A entrada consiste em dois multiplicandos de 8 bits (dataa e datab).

- O multiplicador 8×8 demanda quatro ciclos de clock para executar uma multiplicação completa.

- A multiplicação será feita em partes, por um multiplicador de 4×4 bits, da seguinte forma:

- O multiplicando dataa será dividido em duas fatias de quatro bits “a[7..4]” e “a[3..0]”.

- O multiplicando datab será dividido em duas fatias de quatro bits “b[7..4]” e “b[3..0]”.

- A cada ciclo de clock, o multiplicador de 4×4 bits irá multiplicar um par de fatias e irá somando o resultado da operação.

- Ao final da operação, no quinto ciclo de clock, o resultado da operação será apresentado em 16 bits na saída “product8x8_out”.

- O circuito deve ter um bit indicador de conclusão de operação “done_flag” e sete sinais para acionar um display de 7 segmentos “seg_a”, “seg_b”, “seg_c”, “seg_d”, “seg_e”, “seg_f”, e “seg_g”.

Caso minhas notas sejam de grande valia para ti, vou ficar muito agradecido se você clicar nos anúncios desta página e conferir o que meus patrocinadores tem para lhe oferecer.

A equação abaixo ilustra o princípio desta operação:

product8x8_out[15..0] = ( dataa[7..0] * datab[7..0] ) product8x8_out[15..0] = ( (a[7..4]*24) + (a[3..0]*20) ) * ( (b[7..4]*24) + (b[3..0]*20) ) = ( (a[7..4] * b[7..4]) * 28 ) + ( (a[7..4] * b[3..0]) * 24 ) + ( (a[3..0] * b[7..4]) * 24 ) + ( (a[3..0] * b[3..0]) * 20 )

A figura abaixo ilustra o diagrama em blocos do multiplicador 8×8:

Nesta resolução, serão construídos cada um dos componentes individuais do multiplicador e por último todos componentes serão reunidos, compilados e testados, formando o multiplicador 8×8.

A configuração do ambiente de desenvolvimento Quartus, de seu simulador Questa e a escolha opcional da placa de desenvolvimento podem ser conferidas na série <Instalando Quartus com Questa, clicando aqui>.

Exercícios:

- Início

- Multiplicador 8×8: Exercício lab1a somador 16bits

- Multiplicador 8×8: Exercício lab1b multiplicador 4 bits

- Multiplicador 8×8: Exercício lab2a 4-bits 2:1 Mux

- Multiplicador 8×8 Exercício lab2b 8-16bit left regb

- Multiplicador 8×8 Exercício lab3 Display 7 segmentos

- Multiplicador 8×8 Exercício lab4a Registrador 16bits

- Multiplicador 8×8 Exercício lab4b Contador 2bits assíncrono

- Multiplicador 8×8 Exercício lab5a State Machine

- Multiplicador 8×8 Exercício lab5b Montagem final

Publicado por Renato de Pierri em 22/nov/2023

Fonte: Manual de exercícios de Introdução ao Verilog, da Intel.