Para quem está acompanhando a série Quartus com Questa, sabe que logo no primeiro capítulo eu expliquei como minha cabeça pensou na hora de escolher uma placa de desenvolvimento para estudar VHDL, no caso utilizando o software Quartus e sua ferramenta de simulação Questa, da Intel.

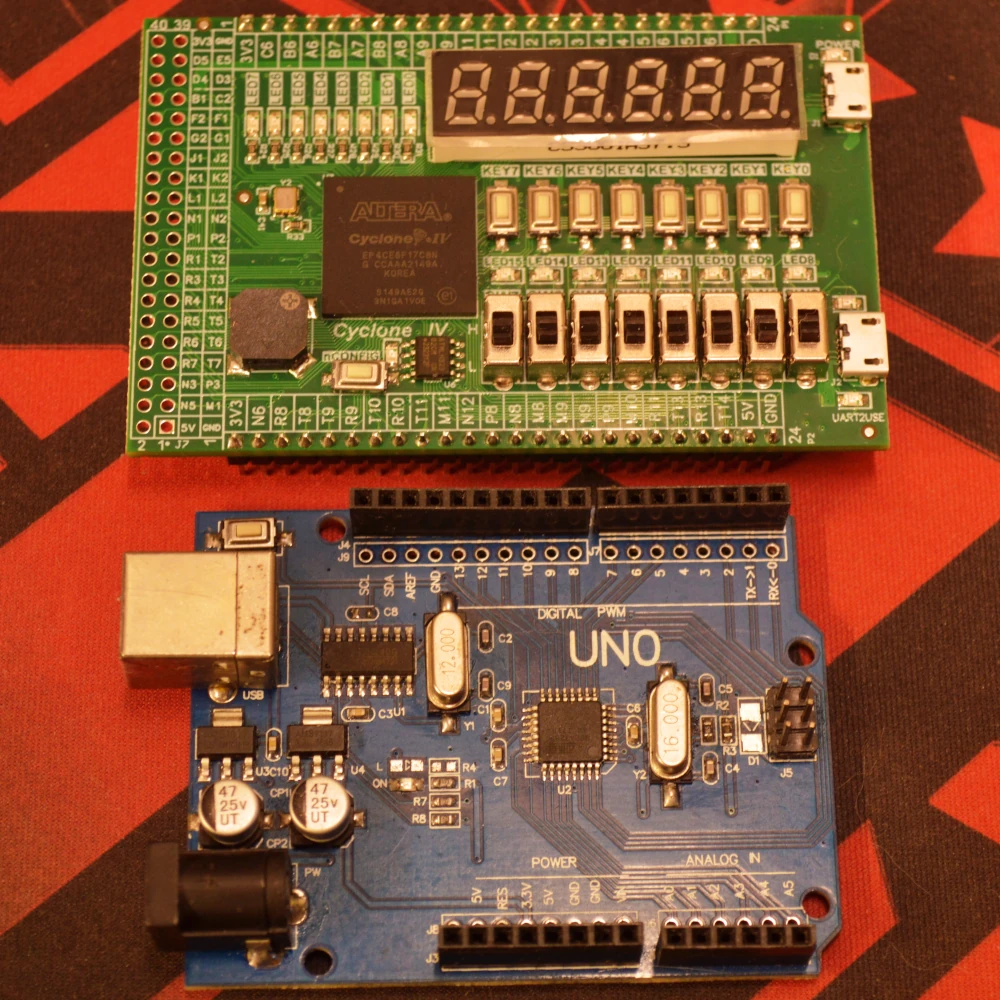

Conforme dito, acabei escolhendo a placa Mini-FPGA que vem com o FPGA Cyclone IV da Intel (que comprou a Altera).

Finalmente chegou!

Caso estas informações sejam de grande valia para ti, vou ficar muito agradecido se você clicar nos anúncios desta página e conferir o que meus patrocinadores tem para lhe oferecer.

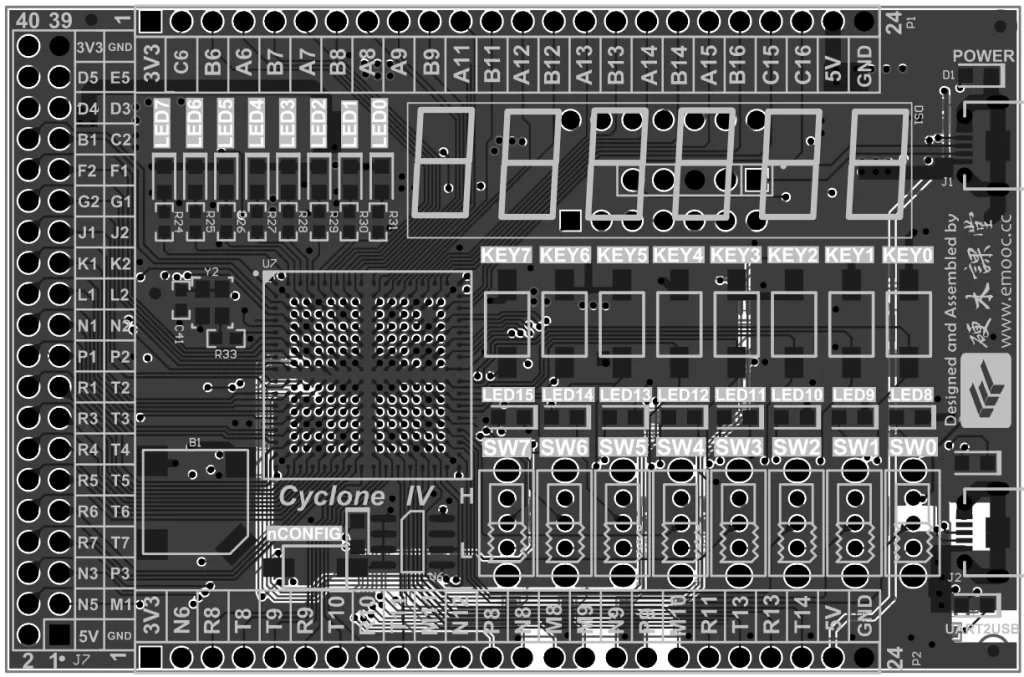

É uma plaquinha de 10,5cm X 7,0cm, um pouco maior que a placa do Arduino Uno e possui trocentos pinos de IO, conforme imagem abaixo:

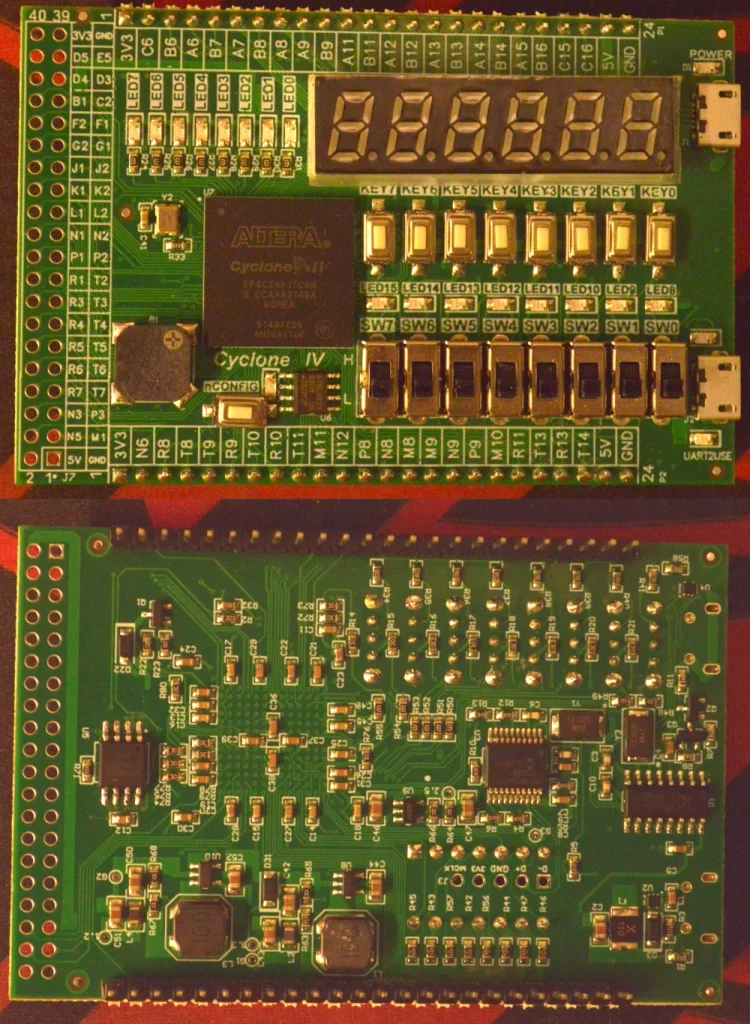

Abaixo temos uma foto ampliada da Mini-FPGA.

A porta USB de cima, perto do led Power é a mini-usb do programador USB Blaster incorporado, o que dispensa a necessidade de se comprar um programador USB-Blaster, sendo que essa entrada USB, serve para programar tanto o FPGA como a memória EEPROM de configuração permanente.

A porta USB de baixo é uma saída USB serial, disponível para uso geral.

A placa pode ser alimentada por qualquer uma das interfaces USB, ou diretamente pela sua pinagem.

Ela possui os seguintes componentes.:

- Cyclone IV EP4CE6F17C8 que contém 256 pinos e 6272 unidades lógicas.

- Memória Flash e EEPROM.

- Um display multiplexado de 6 digitos, 7 segmentos + ponto decimal.

- Um buzzer.

- Entradas e saídas – I/O.

- 8 chaves HH fornecendo os níveis lógicos 1 e 0.

- 16 Leds que ligam com nível 1.

- 8 chaves push-button + 1 chave de reset, todas normalmente em nível lógico 1.

- Interface UART com proteção contra descarga ESD.

- 3 fontes de alimentação de 1.2V, 2.5V e 3.3V para alimentar a placa.

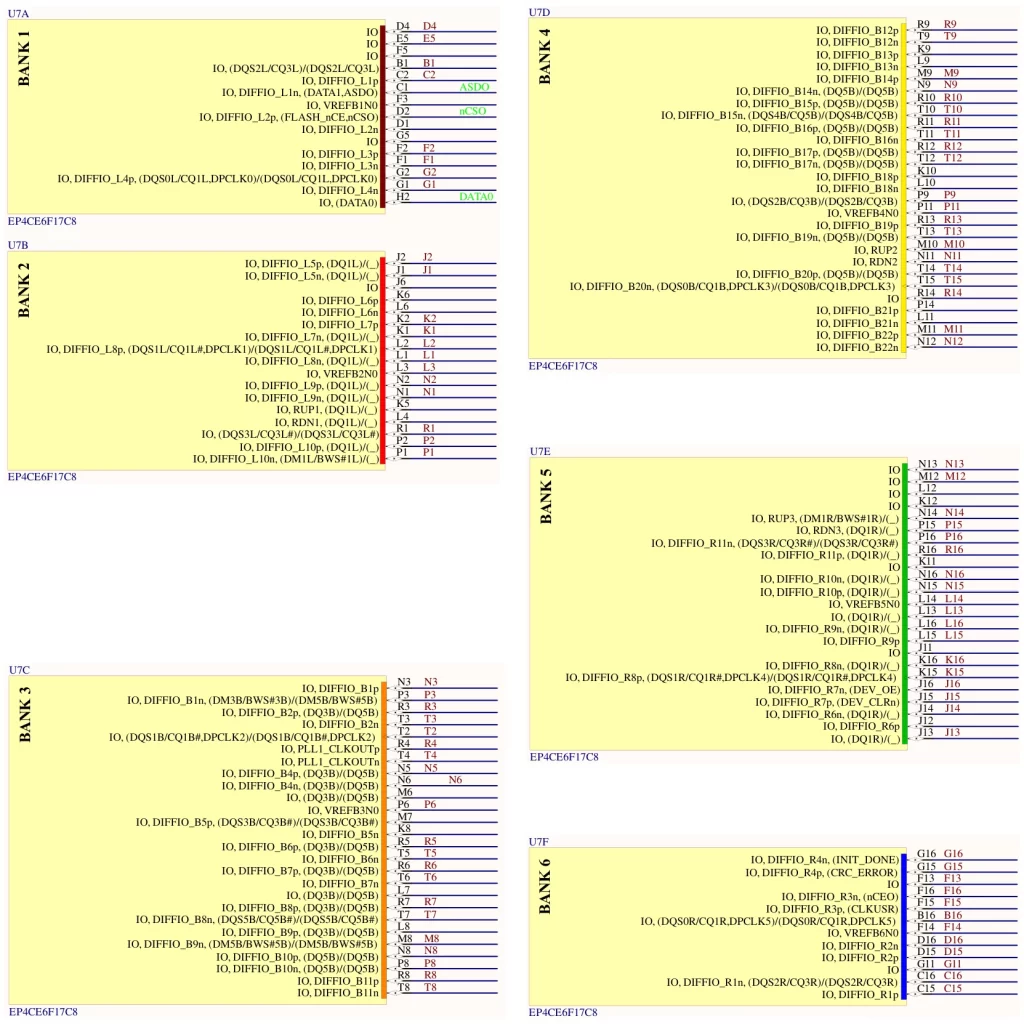

Cyclone IV:

Todos os pinos e periféricos da placa, estão conectados a pinos independentes do FPGA, basta conferir a serigrafia e o diagrama esquemático da placa, que são bem documentados.

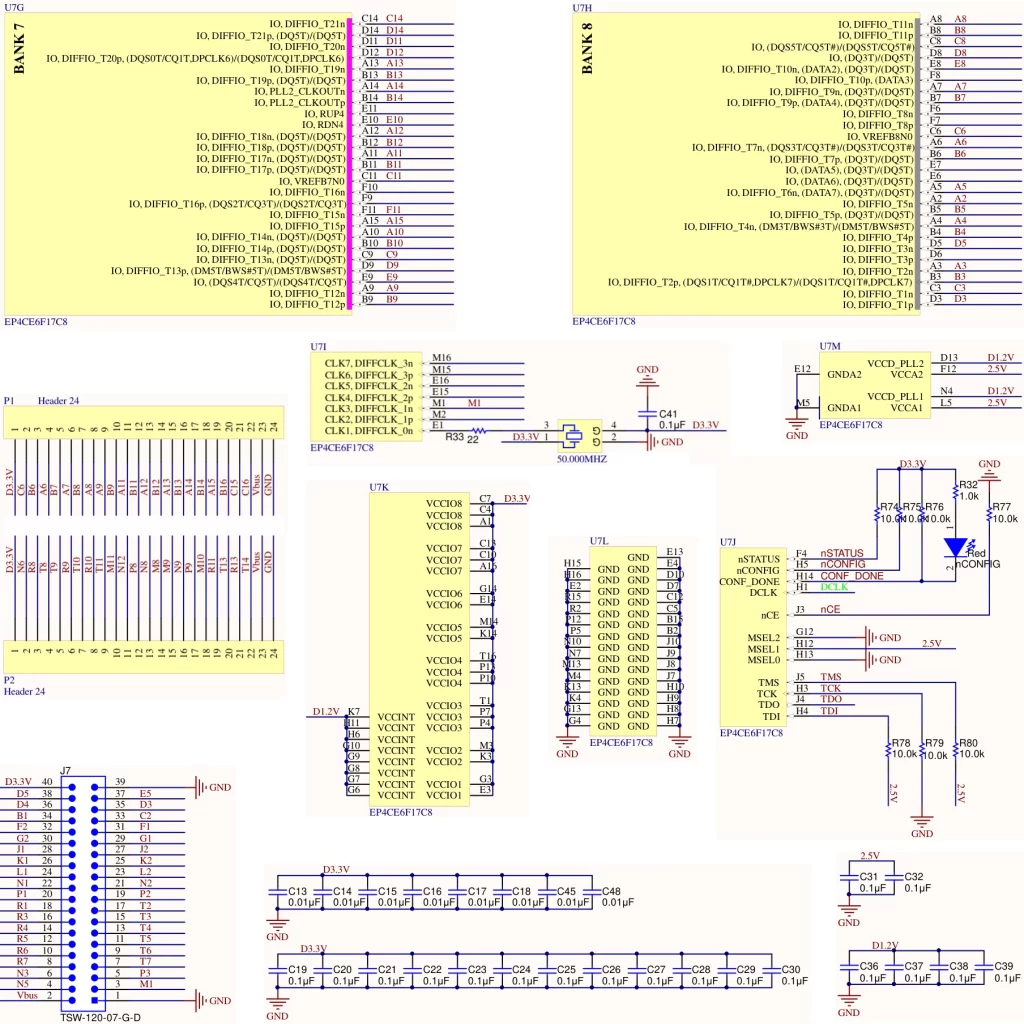

Modo de programação:

O Cyclone IV desta placa utiliza o esquema de configuração “AS / JTAG”, 3,3V no Vccio e com os sinais: MSEL0=0, MSEL1=1, MSEL2=0 e MSEL3=0.

Memória:

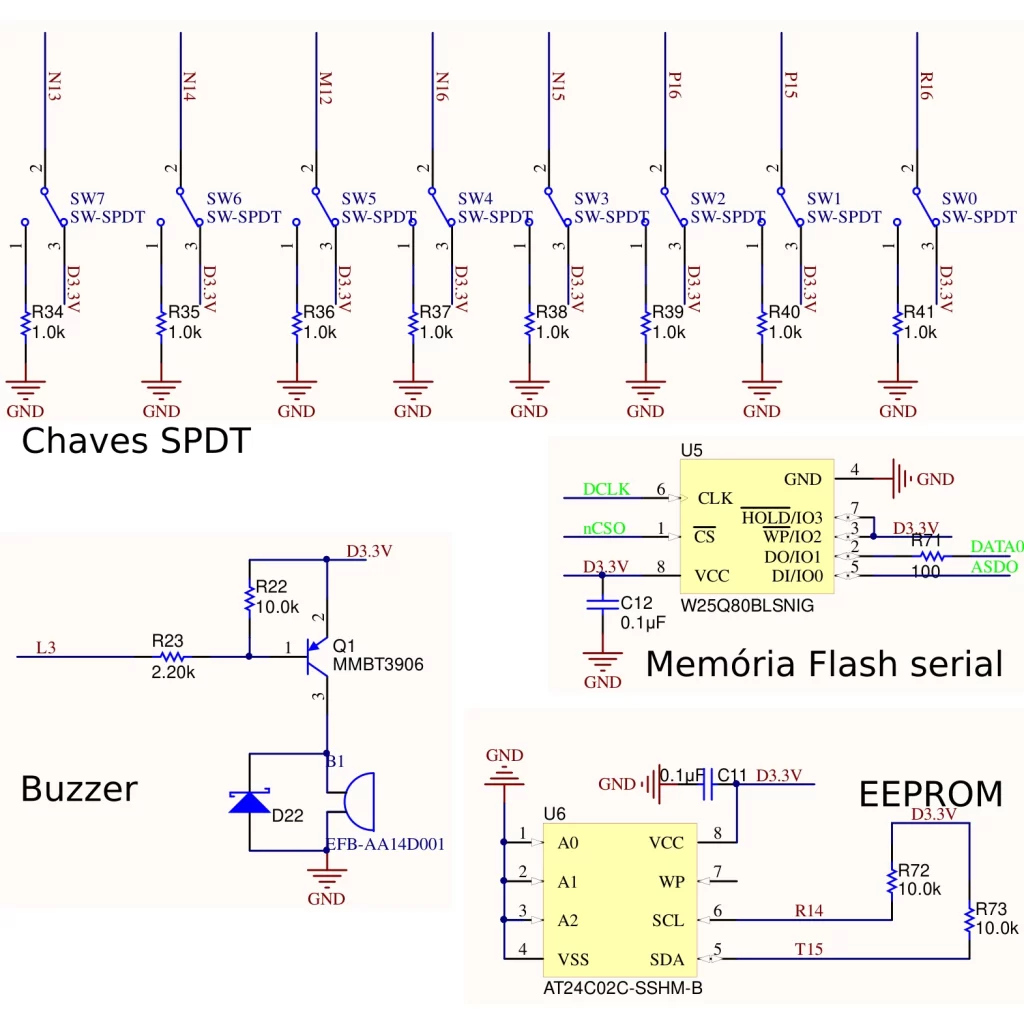

A placa conta com um chip de memória flash serial U5 para armazenar os dados de configuração do FPGA, que são carregados cada vez que a placa de desenvolvimento é ligada ou o botão nConfig é acionado.

Utilizando o software Quartus II, o FPGA pode ser reconfigurado sem modificar os dados salvos na flash ou pode ser configurado em definitivo, alterando os dados de inicialização que são salvos na memória flash.

A placa também conta com um chip de memória EEPROM U6 que utiliza o protocolo I2C. Trata-se de uma memória programável e eletricamente apagável. Os pinos SCL e SDA de U6 são respectivamente conectados aos pinos R14 e T15 do FPGA e pode ser utlizada como memória do sistema.

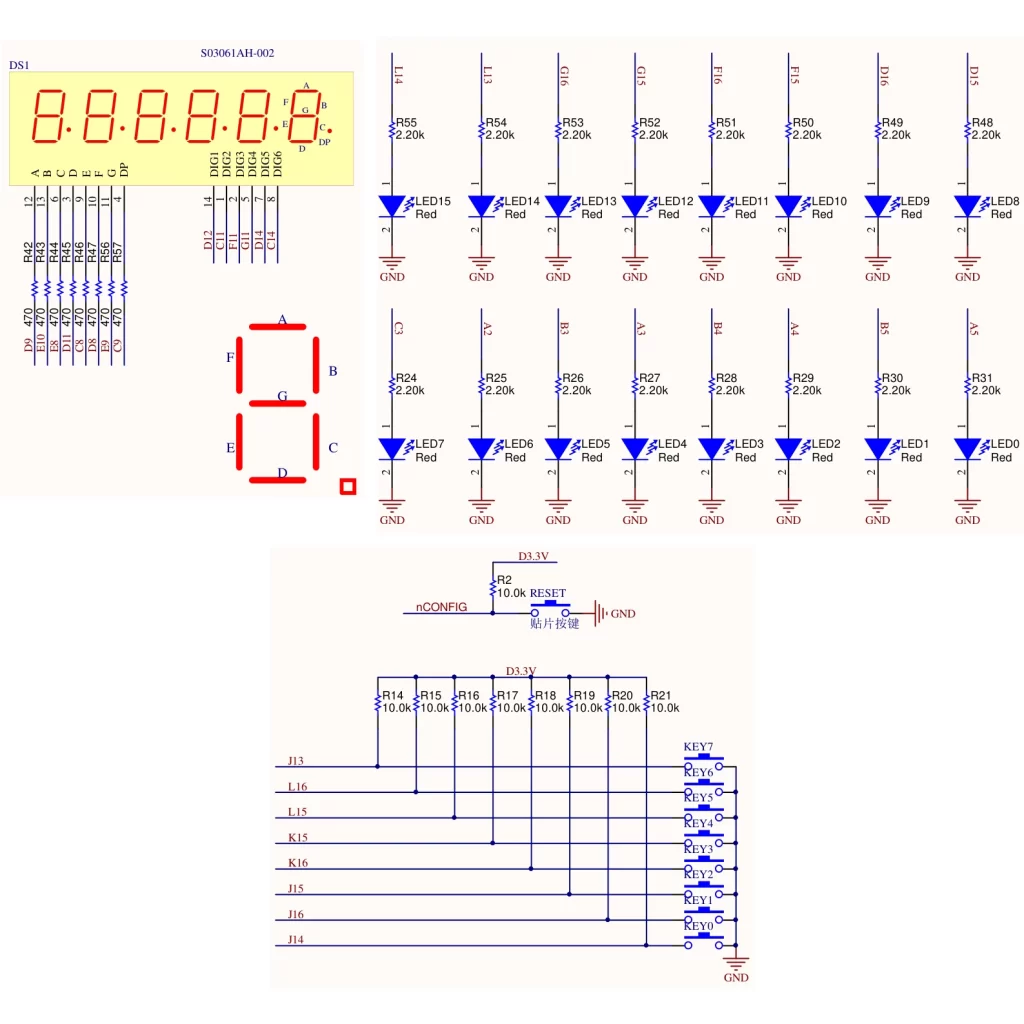

Display:

O display de 7 segmentos + ponto decimal, é um SO3061AS7.3, multiplexado em catodo comum, ou seja:

- Quando a saída do FPGA deve ser alta nas saídas “C9 – ponto decimal”, “E9 – G”, “D8 – F”, “C8 – E”, “D11 – D”, “E8 – C”, “E10 – B” e “D9 – A”, para ligar o respectivo segmento do display.

- As saídas do FPGA “C14 – dig 6”, “D14 – dig 5”, “G11 – dig 4”, “F11 – dig 3″, C11 – dig 2” e “D12 – dig 1” servem para selecionar qual dígito do display, será ligado. Estas saídas estão ativas quando o nível lógico for 0.

Buzzer:

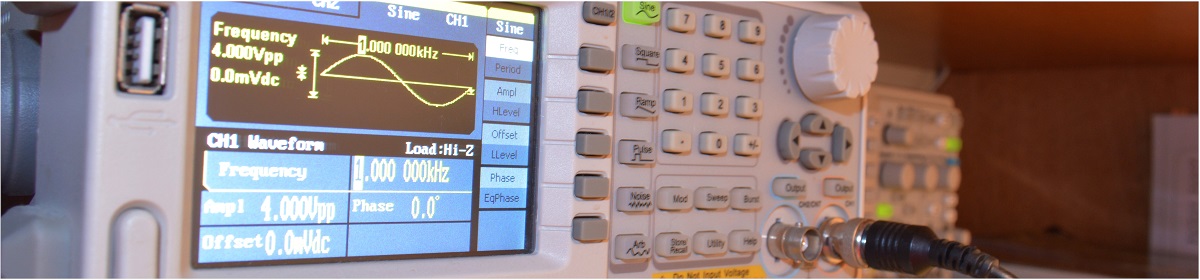

A Mini-FPGA conta com um buzzer cuja tonalidade pode ser ajustada de acordo com a frequência do sinal liberado no pino L3.

Entradas e saídas – I/O:

- Dois conectores de 24 pinos (P1 e P2) com 42 pinos de I/O ligados diretamente ao FPGA, mais as conexões para 5V, 3V3 e GND.

- Um conector de 40 pinos (J7) com 36 pinos conectados diretamente ao FPGA, mais as conexões para 5V, 3V3 e GND.

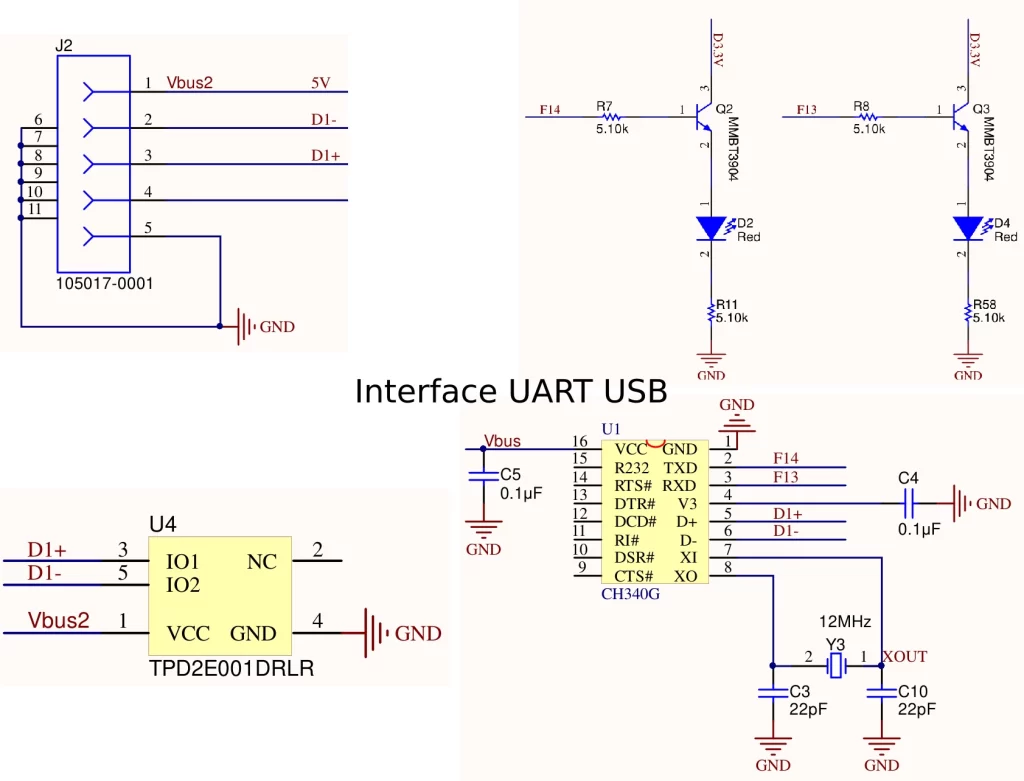

Interface UART/USB:

A placa possui um circuito UART / USB, composto por U1, J2 U4, Q2 e Q3, permitindo usar o cabo de dados USB para conectar ao PC. Os dados USB são convertidos em UART e vice versa, após passarem por este circuito. Deve-se notar que o pino TXD de U5 é conectado ao F14 do FPGA e que o pino RXD de U5, é conectado ao pino F13 do FPGA, ficando a cargo do desenvolvedor a implantação do protocolo de comunicação.

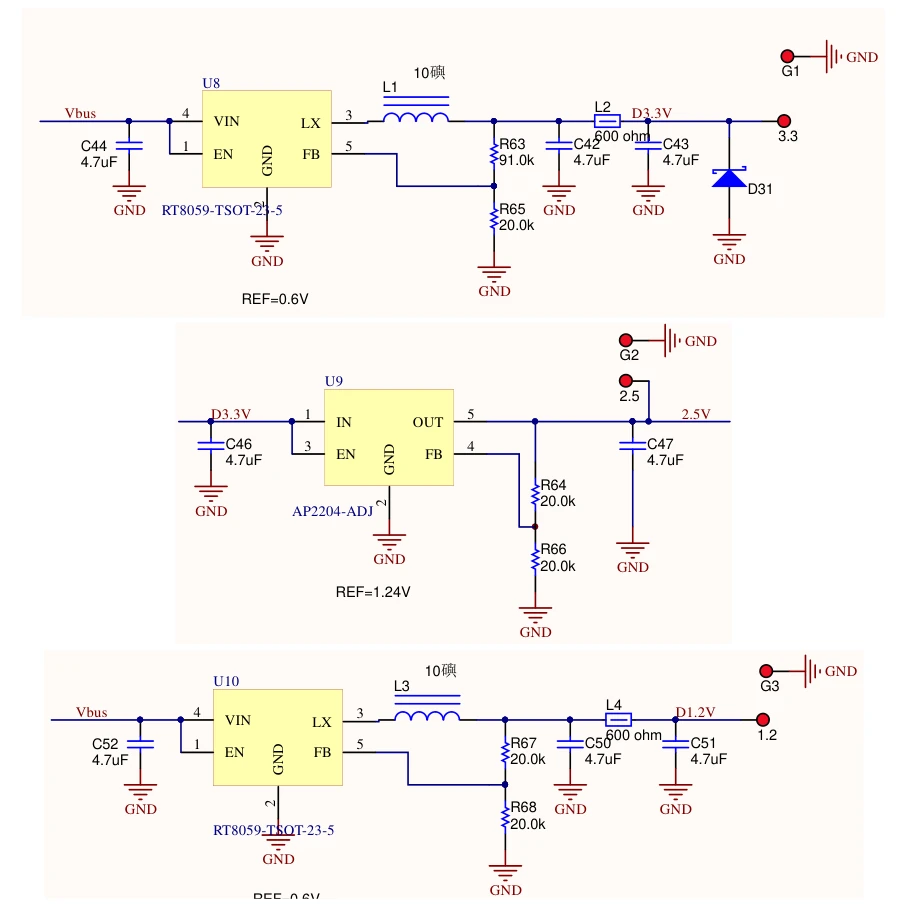

Fontes:

A alimentação do cabo USB provê +5Volts, para pequenas cargas. Dependendo do circuito, uma fonte adicional de 5Volts pode ser necessária.

Os 5Volts do cabo USB são entregues a dois RT8059 U8 e U10 para gerar as tensões de 3,3Volts e 1,2Volts (tensão do núcleo do FPGA). Os 5Volts do cabo USB também alimentam um AP2204 U9, responsável por gerar a tensão de 2,5Volts.

Diagrama esquemático da placa Mini-FPGA

Conforme figura abaixo, temos o circuito da interface USB-Serial

Abaixo temos o esquema de ligação das chaves SPDT, do buzzer, da memória flash serial e da memória EEPROM:

Diagrama esquemático do display, dos leds, dos botões push-button e botão de reset:

Diagrama esquemático do Cyclone IV EP4CE6F17C8:

Fontes de alimentação:

Imagem do layout da placa de circuito impresso:

Publicado por Renato de Pierri em 12/11/2023.

Fonte: www.emooc.cc