Na continuação da construção do multiplicador 8×8, o objetivo desta etapa é construir em Verilog, um “7-segment LED display controller” (controlador de mostrador de led de sete segmentos), utilizando a cláusula de controle “case”, sintetizar e verificar sua operação.

O projeto resolvido desta etapa, pode ser baixado diretamente no github <clicando neste link aqui> e no diretório raiz IVER10_1 temos todos os arquivos e instruções dos exercícios.

Se você caiu de paraquedas por aqui e precisa saber como instalar o software Questa para trabalhar com Verilog, leia a série “Instalando Quartus com Questa”, <clicando neste link aqui>.

Continuando, passos A e B:

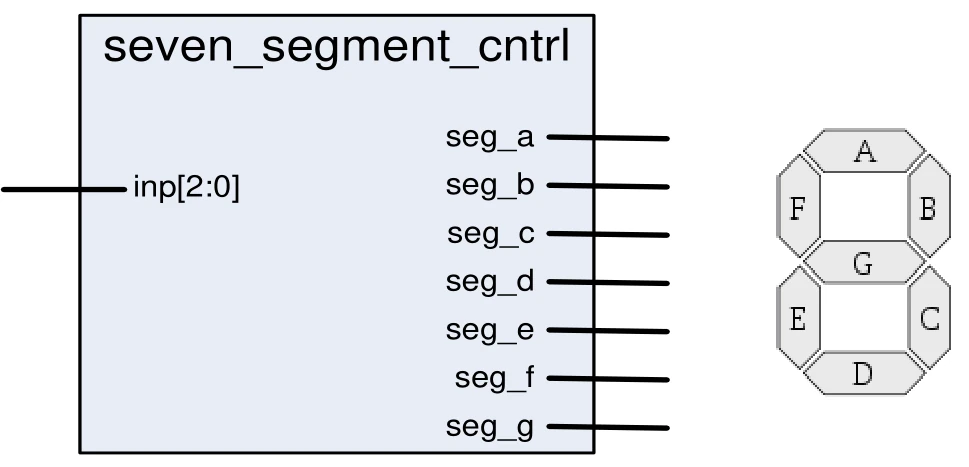

Navegar até a pasta lab3 do diretório dos exercícios, selecionar o arquivo “seven_segment_cntrl.qpf” e abrir com o Quartus, para escrever a descrição de hardware do controlador do display de led de 7 segmentos (7-segment LED display controller) conforme indicado na figura abaixo:

Uma vez aberto o projeto no Quartus, criar um novo arquivo Verilog HDL.

No arquivo verilog hdl, deve ser feita a descrição de um “7-segment display controller” utilizando a declaração comportamental “case” (case behavioral statement), baseado nos seguintes itens:

- O controlador tem uma entrada de dados de 3 bits e 7 saídas binárias, cada uma delas destinadas a controlar um dos segmentos do display.

- As 7 saídas devem se comportar conforme descrito na tabela abaixo:

| Entradas inp[2:0] |

Saídas | Display LED |

||||||

|---|---|---|---|---|---|---|---|---|

| seg_a | seg_b | seg_c | seg_d | seg_e | seg_f | seg_g | ||

| 000 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 001 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 010 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 2 |

| 011 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 3 |

| Outros valores | 1 | 0 | 0 | 1 | 1 | 1 | 1 | E |

- Utilize os nomes da tabela acima para nomear o bloco e os ports, todos em caixa baixa.

- Use o operador de concatenação { } com as saídas para facilitar a atribuição de valores.

- A codificação com behavioral statements sempre demanda o uso de um bloco procedural.

- Todas entradas do bloco procedural, qualquer coisa no RHS de uma atribuição com operador, deve ser listada na lista de eventos do bloco.

A descrição de hardware resolvida deve ficar conforme abaixo:

module seven_segment_cntrl (

input [2:0] inp,

output reg seg_a, seg_b, seg_c, seg_d,

output reg seg_e, seg_f, seg_g,

output catodo_comum_dsp //adicionado para poder ligar o catodo comum do display - so para testes

);

assign catodo_comum_dsp = 0; //sempre zero mantem o display sempre aceso - so para testes

always@ (inp) begin

case(inp)

// 7-segment display apresenta '0' quando entrada é igual a "000"

// 7-segment display apresenta '1' quando entrada é igual a "001"

// 7-segment display apresenta '2' quando entrada é igual a "010"

// 7-segment display apresenta '3' quando entrada é igual a "011"

// 7-segment display apresenta 'E' quando entrada tiver outros valores

3'B000 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b1111110;

3'B001 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b0110000;

3'B010 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b1101101;

3'B011 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b1111001;

default : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b1001111;

endcase

end

endmodule

Caso minhas notas sejam de grande valia para ti, vou ficar muito agradecido se você clicar nos anúncios desta página e conferir o que meus patrocinadores tem para lhe oferecer.

Passo C:

Nesta etapa deve-se sintetizar o projeto no Quartus, no menu “Processing” -> “Start” -> “Start Analysis & Synthesis” até que o compilador retorne a mensagem “Analysis & Synthesis was successful”.

Corrigir eventuais erros que venham a aparecer.

Passo D:

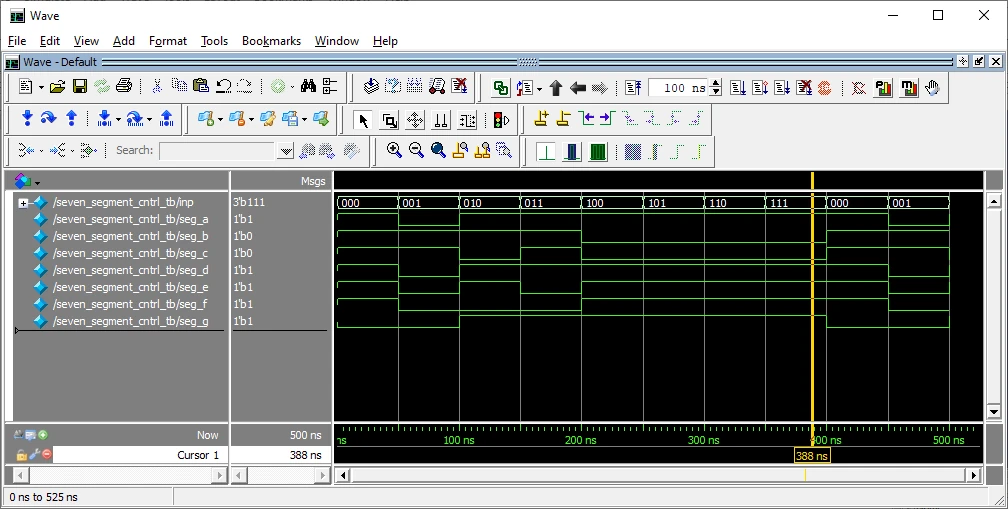

Executar a simulação RTL. Nesta parte, deve-se iniciar o simulador Questa para verificar a funcionalidade do projeto. Para isso, precisa abrir o arquivo de teste chamado “seven_segment_cntrl_tb.v” que foi criado para fornecer os vetores de teste da simulação.

- Inicie o Questa e troque para o diretório “lab3”, conforme explicado nos exercícios anteriores.

- Em seguida execute a macro “seven_segment_cntrl_tb.do” conforme indicado em exercícios anteriores.

- A janela da forma de onda irá abrir com os sinais de entrada “input” e os de saída “seg_*”, permitindo a verificação da funcionalidade da descrição de hardware criada, conforme imagem indicada abaixo:

Caso a simulação não se comporte conforme indicado acima, verifique o exercício e faça as devidas correções.

Resumo do exercício:

Foi codificado um controlador de display de led de 7 segmentos utilizando Verilog, empregando a declaração comportamental “case” e em seguida foi verificada a funcionalidade, utilizando o software Questa.

Implementando e testando na Mini-FPGA, o bloco display de 7 segmentos

Os passos a seguir são específicos para a placa de desenvolvimento Mini-FPGA utilizando o Cyclone IV EP4CE6F17C8. Caso esteja utilizando outra placa de desenvolvimento, os devidos ajustes devem ser realizados.

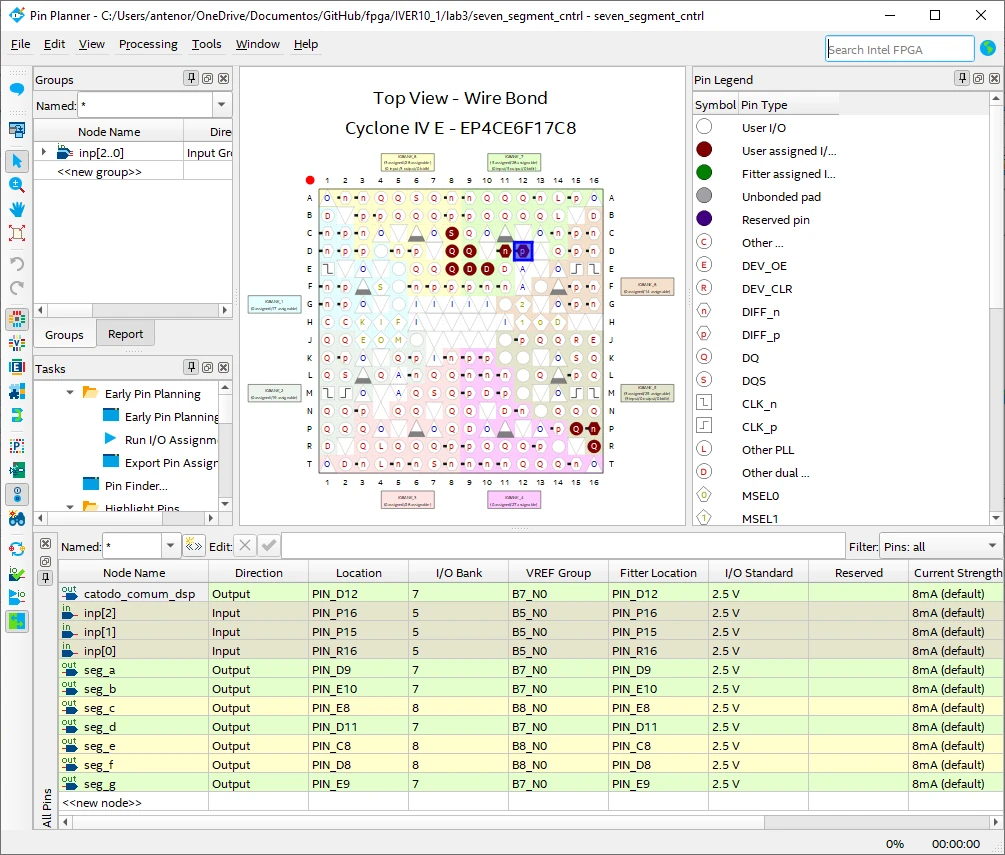

Feito os testes, para subir a descrição de hardware para a placa de desenvolvimento, é necessário planejar o pin planner de acordo com o diagrama esquemático da placa Mini-FPGA, <que pode ser consultado neste link aqui>.

Os pinos devem ser configurados conforme abaixo:

| inp[2] – PIN_J15 | inp[1] – PIN_J16 | inp[0] – PIN_J14 |

| seg_a – PIN_D9 | seg_b – PIN_E10 | seg_c – PIN_E8 |

| seg_d – PIN_D11 | seg_e – PIN_C8 | seg_f – PIN_D8 | seg_g – PIN_E9 |

| catodo_comum_dsp – PIN_D12 |

Abaixo segue o print de tela da configuração do pin planner:

- Multiplicador 8×8: Exercício lab1a somador 16bits

- Multiplicador 8×8: Exercício lab1b multiplicador 4 bits

- Multiplicador 8×8: Exercício lab2a 4-bits 2:1 Mux

- Multiplicador 8×8 Exercício lab2b 8-16bit left regb

- Multiplicador 8×8 Exercício lab3 Display 7 segmentos <-

- Multiplicador 8×8 Exercício lab4a Registrador 16bits

- Multiplicador 8×8 Exercício lab4b Contador 2bits assíncrono

- Multiplicador 8×8 Exercício lab5a State Machine

- Multiplicador 8×8 Exercício lab5b Montagem final

Realizado por Renato de Pierri em 01/12/2023.

Fonte: Manual de exercícios de Introdução ao Verilog, da Intel.