Na continuação da construção do multiplicador 8×8, o objetivo desta etapa é construir em Verilog, um “16-bit register with synchronous control” (registrador de 16bits com controle síncrono) utilizando o “sequential process” (processo sequencial), sintetizar e verificar a sua operação.5

O projeto resolvido desta etapa, pode ser baixado diretamente no github <clicando neste link aqui> e no diretório raiz IVER10_1 temos todos os arquivos e instruções dos exercícios.

Se você caiu de paraquedas por aqui e precisa saber como instalar o software Questa para trabalhar com Verilog, leia a série “Instalando Quartus com Questa”, <clicando neste link aqui>.

Passos A e B:

Abra o Quartus e o projeto do registrador: “File” -> “Open Project” -> Navegue até a pasta “lab4a” -> selecione e abra com o Quartus, o arquivo “reg16.qpf”.

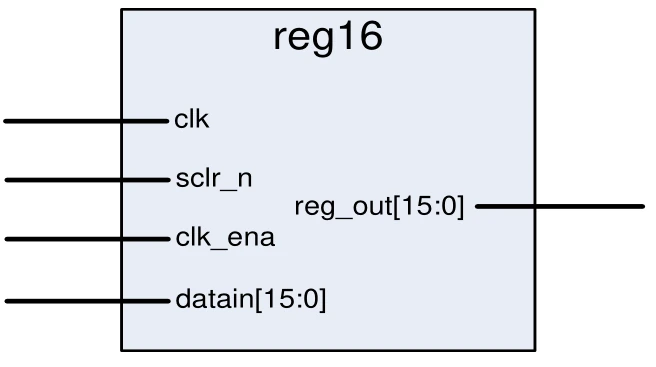

Uma vez aberto o projeto, é hora de codificar o bloco do registrador 16 bits, cujo diagrama pode ser visto na figura abaixo:

No projeto, crie um arquivo Verilog HDL, conforme ensinado anteriormente e escreva a descrição de hardware de um “16-bit register with synchronous control” utilizando o “sequential process, tendo as informações abaixo como orientação:

O registrador deve ter:

- Tamanho de 16 bits de entrada e de saída,

- Clock de entrada,

- Clear síncrono,

- Um sinal para habilitar o clock que opere em modo síncrono.

Caso minhas notas sejam de grande valia para ti, vou ficar muito agradecido se você clicar nos anúncios desta página e conferir o que meus patrocinadores tem para lhe oferecer.

O comportamento do registrador deve ser conforme:

- Todas transações ocorrem na borda de subida do “clk” (clock).

- Após detectar a borda de subida do “clk”, precisa verificar se o sinal “clk_ena” está alto.

- Se o sinal “clk_ena” estiver alto, precisa verificar se “sclr_n” é baixo. Se for, a saída do registrador deve ser apagada.

- Se os sinais “clk_ena” e “scl_clr” estiverem altos, então a saída do registrador deve receber o valor da entrada do registrador.

- O registrador não deve aceitar qualquer comando se o sinal “clk_ena” estiver baixo.

- Utilize nomes do diagrama acima para nomear a sua descrição de hardware e portas, sempre utilizando caixa baixa.

- Os controles síncronos não devem ser incluídos na lista e eventos (sensivity list).

- A menos que explicitamente modificado, as saídas procedurais irão reter seus valores da execução prévia.

Salve o arquivo como “reg16.v” e ele deve ficar no diretório “lab4a”.

Segue abaixo um exemplo da descrição de hardware:

module reg16 ( input [15:0] datain, input clk, sclr_n, clk_ena, output reg [15:0] reg_out ); // Criando o processo sequencial, sensível ao clock e utilizando // declarações if-else aninhadas para habilitar o clock síncrono e // controle de clear. always@(posedge clk) begin if (clk_ena) if(!sclr_n) reg_out <= 16'b0 ; else reg_out <= datain; end endmodule

Passo D – Executar a simulação RTL:

Nesta etapa será verificada a funcionalidade do projeto. O exercício já tem um arquivo de testes, uma macro, criada para verificar se tudo está certinho.

Abra o Questa, e troque o diretório para o local do projeto “lab4a” e em seguida execute a macro, clicando em “Tools” -> “Tcl” -> “Execute Macro”, selecionando o arquivo de macro”reg16_tb.do” e clicando em “Open”.

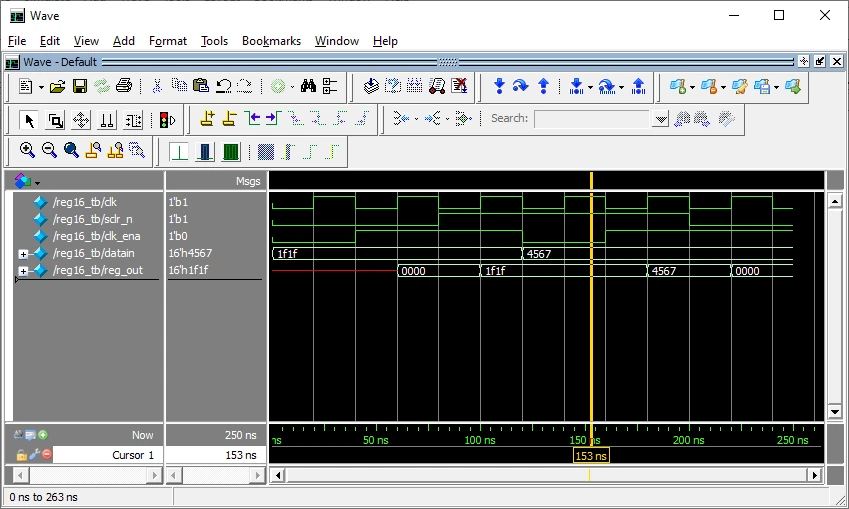

Após rodar a macro, a tela Wave deve ficar conforme imagem abaixo:

Caso o resultado não seja conforme a tela acima, reveja os passos anteriores até obter o resultado esperado.

Nesta etapa foi codificado um “16-bit register with synchronous control” em Verilog, utilizando um “sequential procedural block” (bloco de procedimentos sequenciais) e foi verificado o seu correto funcionamento no Questa.

Feche a simulação.

Implementando e testando na Mini-FPGA, o registrador de 16bits com controle síncrono.

Os passos a seguir são específicos para a placa de desenvolvimento Mini-FPGA utilizando o Cyclone IV EP4CE6F17C8.

Caso esteja utilizando outra placa de desenvolvimento, os devidos ajustes devem ser realizados.

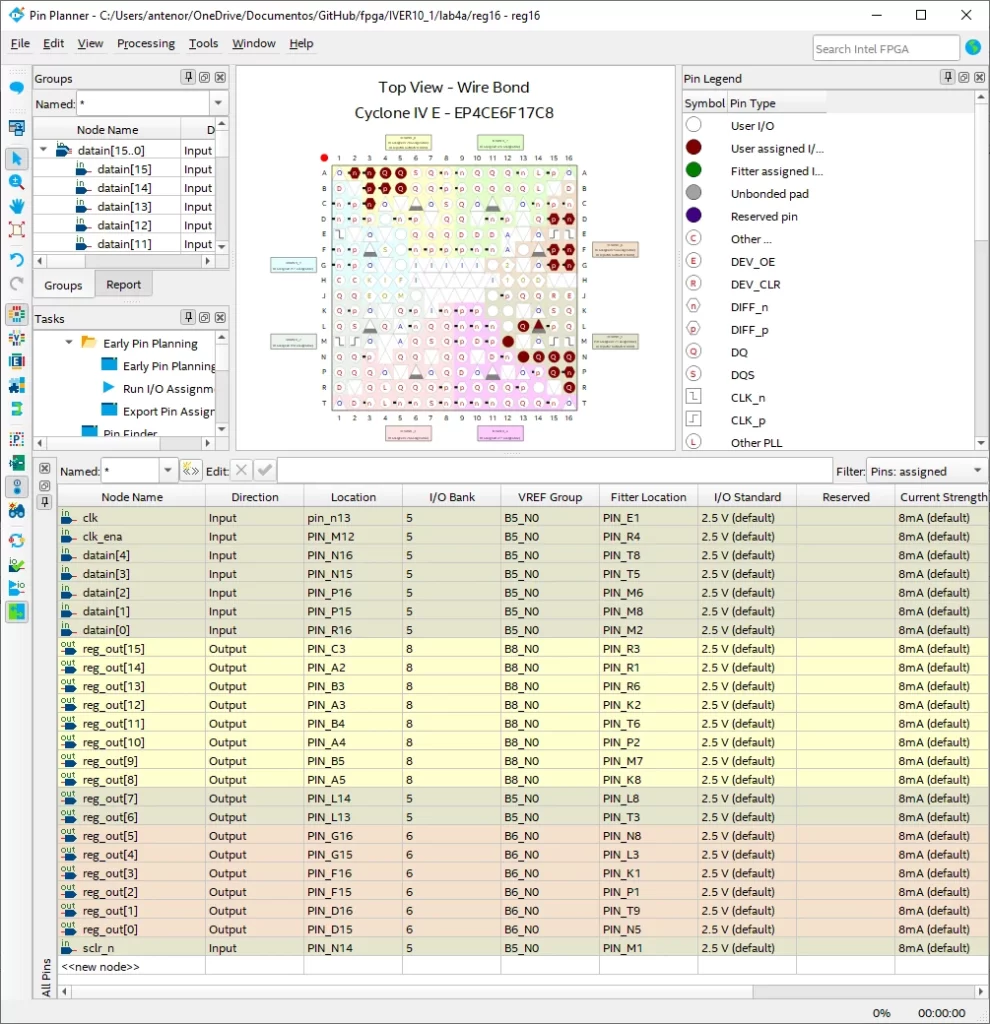

Feito os testes, para subir a descrição de hardware para a placa de desenvolvimento, é necessário planejar o pin planner de acordo com o diagrama esquemático da placa Mini-FPGA, <que pode ser consultado neste link aqui>.

Considerações:

Os sinais “clk”, “sclr_n”, “clk_ena” e “datain[15:0]” representam 18 bits de entrada e a placa Mini-FPGA não tem todas as chaves necessárias para fazer o teste.

262144 combinações possíveis de teste:

Para elaborar um teste completo, precisaria usar os pinos de I/0 externos e montar um hardware adicional, ou elaborar no Questa, um programa que teste todas as possibilidades que esse circuito pode fazer. A própria Intel não fez isso na simulação RTL listada acima -.-

Simplificando:

Para as coisas continuarem simples, também vou fazer um teste parcial utilizando apenas os recursos da placa Mini-FPGA, lembrando que opções de testes mais elaboradas podem ser desenvolvidas, tanto em hardware como usando o Questa.

Desta forma vou distribuir os sinais da seguinte forma, na placa Mini-FPGA:

- Cinco chaves SW[0:4] vão representar 5 bits LSB dos dados de entrada “datain”.

- Chave SW5 vai representar o sinal “clk_ena”.

- Chave SW6 vai representar o sinal “sclr_n”.

- Chave SW7 vai representar o sinal “clk”.

- Leds “Led[0:15]” vão representar a saída “reg_out[15:0]”

Conforme configuração indicada abaixo:

| datain[4] - PIN_N16 | datain[3] - PIN_N15 | datain[2] - PIN_P16 | datain[1] - PIN_P15 | datain[0] - PIN_R16 |

| clk_ena - PIN_M12 | sclr_n - PIN_N14 | clk - PIN_N13 |

| reg_out[0] - PIN_D15 | reg_out[1] - PIN_D16 | reg_out[2] - PIN_F15 | reg_out[3] - PIN_F16 |

| reg_out[4] - PIN_G15 | reg_out[5] - PIN_G16 | reg_out[6] - PIN_L13 | reg_out[7] - PIN_L14 |

| reg_out[8] - PIN_A5 | reg_out[9] - PIN_B5 | reg_out[10] - PIN_A4 | reg_out[11] - PIN_B4 |

| reg_out[12] - PIN_A3 | reg_out[13] - PIN_B3 | reg_out[14] - PIN_A2 | reg_out[15] - PIN_C3 |

Abaixo segue o print de tela da configuração do pin planner:

- Multiplicador 8×8: Exercício lab1a somador 16bits

- Multiplicador 8×8: Exercício lab1b multiplicador 4 bits

- Multiplicador 8×8: Exercício lab2a 4-bits 2:1 Mux

- Multiplicador 8×8 Exercício lab2b 8-16bit left regb

- Multiplicador 8×8 Exercício lab3 Display 7 segmentos

- Multiplicador 8×8 Exercício lab4a Registrador 16bits <-

- Multiplicador 8×8 Exercício lab4b Contador 2bits assíncrono

- Multiplicador 8×8 Exercício lab5a State Machine

- Multiplicador 8×8 Exercício lab5b Montagem final

Publicado por Renato de Pierri em 01/12/2023.

Fonte: Manual de exercícios de Introdução ao Verilog, da Intel.