Na continuação da construção do multiplicador 8×8, o objetivo desta etapa é construir em Verilog, um “2-bit counter with asynchronous control” (contador de dois bits com controle assíncrono), sintetizar e verificar a sua operação.

O projeto resolvido desta etapa, pode ser baixado diretamente no github <clicando neste link aqui> e no diretório raiz IVER10_1 temos todos os arquivos e instruções dos exercícios.

Se você caiu de paraquedas por aqui e precisa saber como instalar o software Questa para trabalhar com Verilog, leia a série “Instalando Quartus com Questa”, <clicando neste link aqui>.

Passos A e B:

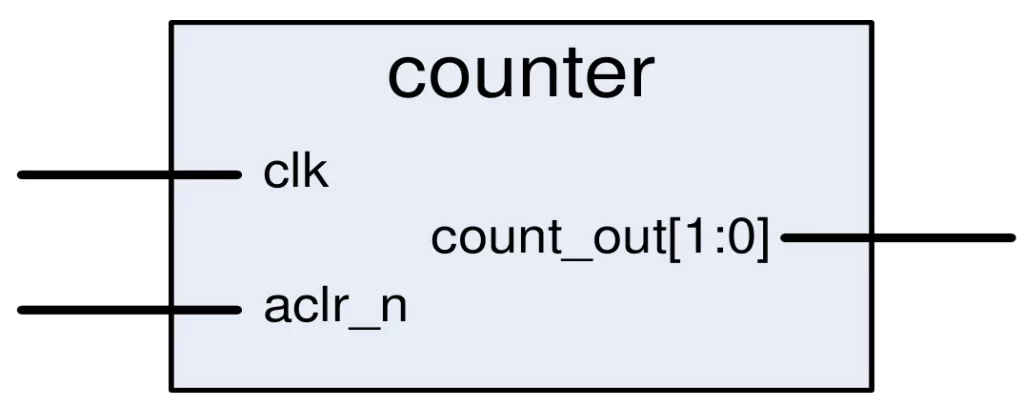

Abra o projeto do contador no Quartus. Para isso, navegue até o diretório <Projeto Diretório>\lab4b e escolha Abrir projeto ao selecionar o arquivo “counter.qpf” para codificar o contador de 2 bits com controle assíncrono, conforme figura abaixo:

No Quartus crie no projeto counter, o arquivo verilog a partir do menu “File” -> “New”” -> “Verilog HDL file” -> “Ok” e monte o “2-bit counter with assynchronous control” utilizando o processo sequencial, conforme indicações a seguir:

- O registrador possui um clock, um “clear” assíncrono e uma saída de dados de 2 bits.

- A saída do contador deve ir para 00 imediatamente quando “aclr_n” está baixo.

- Se “aclr_n” for alto, a saída do contador incrementa 1 cada vez que tiver uma subida no pulso de “clk”.

- Use os nomes do diagrama acima para descrever o circuito e suas portas, sempre com todas em letras minúsculas.

- A checagem dos sinais do “asynchronous register control” em um bloco processual sequencial, deve ocorrer primeiro.

- Os controles assíncronos devem ser incluídos na lista de eventos (lista de sensibilidade).

Abaixo temos um exemplo de como esse código deve ficar:

module counter (

input clk, aclr_n,

output reg [1:0] count_out

);

// Cria um processo sequencial sensível ao clock, com clear assíncrono.

// Utilizando a instrução "if-else" para testar primeiro a atuação do sinal de controle assíncrono.

// A contagem na borda ascendente do clock não irá acontecer, caso o clear esteja ativo.

always@(posedge clk, negedge aclr_n) begin

if (aclr_n == 1'b0)

count_out <= 2'b0;

else

count_out <= count_out + 1'b1;

end

endmodule

Caso minhas notas sejam de grande valia para ti, vou ficar muito agradecido se você clicar nos anúncios desta página e conferir o que meus patrocinadores tem para lhe oferecer.

Passo C, Sintetizando:

Salve o arquivo como “counter.v” na pasta “lab4b” do diretório do projeto e proceda com a síntese e análise do mesmo, clicando em “Start” -> “Start Analysis & Synthesis.

Corrija todos os erros até que a janela de status da compilação apresente a mensagem: “Analysis & Synthesis was successful”.

Passo D, Executando a simulação RTL:

Utilize o Questa para verificar a funcionalidade do projeto.

Abra o Questa, selecione o menu “File” -> “Change Directory” -> e navegue até a pasta do projeto, que deve estar no diretório lab4b e clique em “Selecionar a pasta”.

Feito isso, rode o arquivo de macro “counter_tb.do” pelo menu “Tolls” -> “Tcl” -> “Execute macro” -> selecione o arquivo “counter_tb.do” -> e clique no botão “Abrir”.

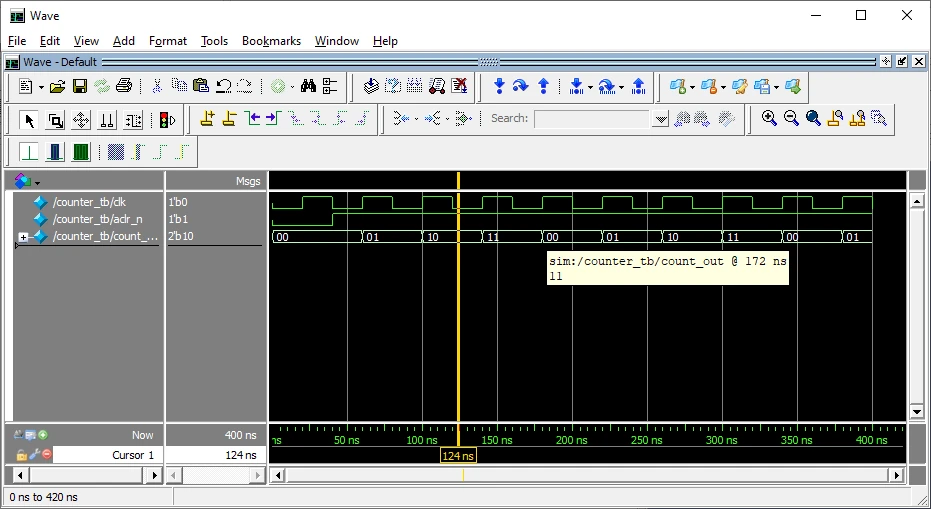

A macro será executada e o Questa deve apresentar a tela de simulação Wave, conforme indicado abaixo:

Confira os resultados da simulação para ver se batem com a figura acima. Caso sua simulação tenha ficado diferente, precisa revisar os passos anteriores até que a saída fique conforme print de tela acima.

Implementando e testando na Mini-FPGA, o contador 2bits assíncrono.

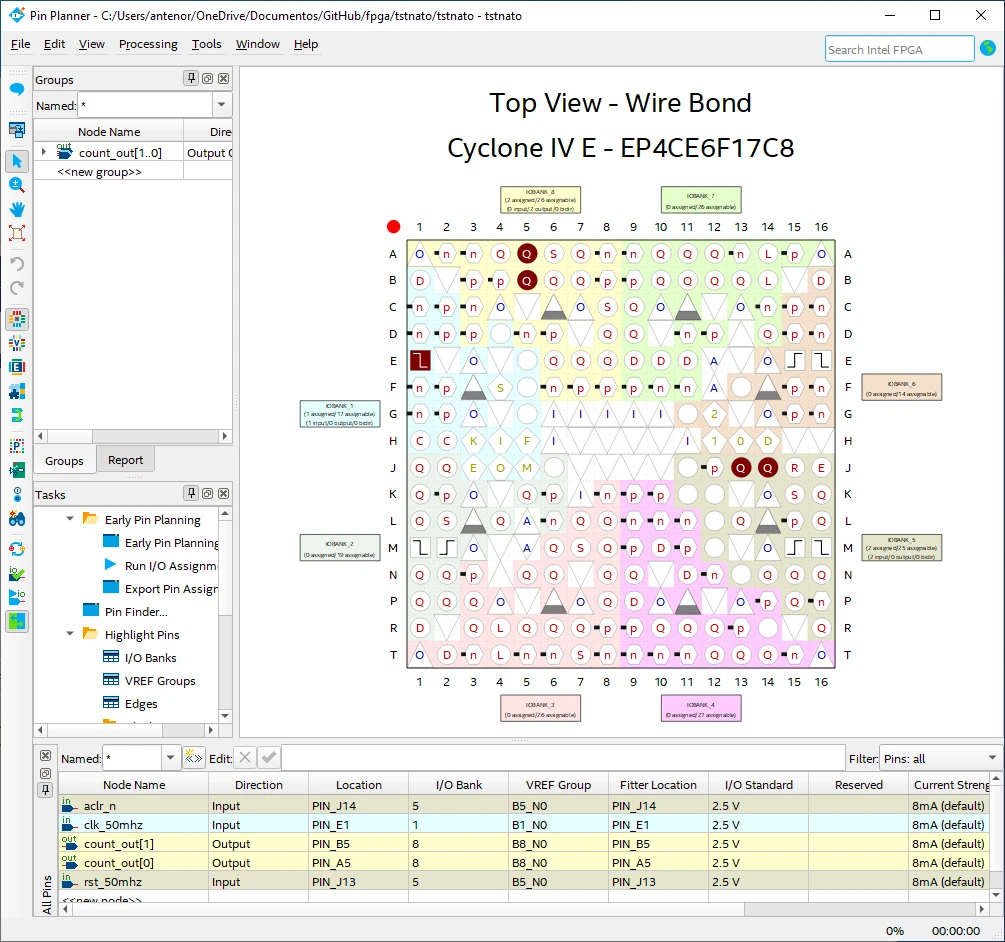

Os passos a seguir são específicos para a placa de desenvolvimento Mini-FPGA utilizando o Cyclone IV EP4CE6F17C8.

Caso esteja utilizando outra placa de desenvolvimento, os devidos ajustes devem ser realizados.

Feito os testes, para subir a descrição de hardware para a placa de desenvolvimento, é necessário planejar o pin planner de acordo com o diagrama esquemático da placa Mini-FPGA, <que pode ser consultado neste link aqui>.

Considerações:

Este bloco possui os sinais “clk”, “aclr_n”, “count_out[1:0]” do contador, e os sinais “clk_50Mhz” e “rst_50Mhz” para testar o contador. Esses sinais de teste, linhas 7 ao 25 e a declaração dos sinais, serão removidos no circuito final do multiplicador.

Abaixo temos a descrição de hardware do contador com o circuito de teste:

module tstnato(

input clk_50mhz,rst_50mhz, //gerador de clock 0,5hz - 1 segundo alto, 1 segundo baixo

aclr_n,

output reg [1:0] count_out

);

// Gerador de clock para testes

reg [25:0] count_reg = 0;

reg out_1hz = 0;

reg clk;

always @(posedge clk_50mhz or negedge rst_50mhz) begin

if (rst_50mhz == 0) begin

count_reg <= 0;

out_1hz <= 0;

end else begin

if (count_reg < 50000000) begin

count_reg <= count_reg + 1;

end else begin

count_reg <= 0;

out_1hz <= ~out_1hz;

clk <= out_1hz; // Aqui o clock é injetado no somador

end

end

end

//Fim do gerador de clock

// Somador de 2 bits

// Cria um processo sequencial sensível ao clock, com clear assíncrono.

// Utilizando a instrução "if-else" para testar primeiro a atuação do sinal de controle assíncrono.

// A contagem na borda ascendente do clock não irá acontecer, caso o clear esteja ativo.

always@(posedge clk, negedge aclr_n) begin

if (aclr_n == 1'b0)

count_out <= 2'b0;

else

count_out <= count_out + 1'b1;

end

endmodule

O circuito de teste pega o sinal de 50Mhz e divide por 50 milhões, gerando o sinal de teste “out_1hz” que é um clock de 0,5hertz (1 segundo nível alto e 1 segundo nível baixo).

O sinal de teste “out_1hz” é injetado no sinal “clk” e o resto do contador é o mesmo do circuito do contador.

A partir da descrição acima, temos abaixo o mapeamento da pinagem e o respectivo print do pin planner:

|clk_50Mhz – PIN_E1|rst_50Mhz – PIN_J13|aclr_n – PIN_J14|count_out[1] – PIN_B5|count_out[0] – PIN_A5|

- Multiplicador 8×8: Exercício lab1a somador 16bits

- Multiplicador 8×8: Exercício lab1b multiplicador 4 bits

- Multiplicador 8×8: Exercício lab2a 4-bits 2:1 Mux

- Multiplicador 8×8 Exercício lab2b 8-16bit left regb

- Multiplicador 8×8 Exercício lab3 Display 7 segmentos

- Multiplicador 8×8 Exercício lab4a Registrador 16bits

- Multiplicador 8×8 Exercício lab4b Contador 2bits assíncrono <-

- Multiplicador 8×8 Exercício lab5a State Machine

- Multiplicador 8×8 Exercício lab5b Montagem final

Realizado por Renato de Pierri em 02/12/2023

Fonte: Manual de exercícios de Introdução ao Verilog, da Intel.